ГОСТ 26.201.2-94

(МЭК 640-79)

МЕЖГОСУДАРСТВЕННЫЙ СТАНДАРТ

СИСТЕМА КАМАК

ПОСЛЕДОВАТЕЛЬНАЯ МАГИСТРАЛЬ

ИНТЕРФЕЙСНОЙ СИСТЕМЫ

МЕЖГОСУДАРСТВЕННЫЙ СОВЕТ

ПО СТАНДАРТИЗАЦИИ, МЕТРОЛОГИИ И СЕРТИФИКАЦИИ

Минск

Предисловие

1 РАЗРАБОТАН МТК 233 «Измерительная аппаратура для основных электрических величин».

ВНЕСЕН Госстандартом Российской Федерации.

2 ПРИНЯТ Межгосударственным Советом по стандартизации, метрологии и сертификации (протокол № 6-94 от 21 октября 1994 г.)

За принятие проголосовали:

|

Наименование государства |

Наименование национального органа по стандартизации |

|

Азербайджанская Республика |

Азгосстандарт |

|

Республика Армения |

Армгосстандарт |

|

Республика Беларусь |

Белстандарт |

|

Республика Грузия |

Грузстандарт |

|

Республика Казахстан |

Госстандарт Республики Казахстан |

|

Кыргызская Республика |

Кыргызстандарт |

|

Республика Молдова |

Молдовастандарт |

|

Российская Федерация |

Госстандарт России |

|

Республика Узбекистан |

Узгосстандарт |

|

Украина |

Госстандарт Украины |

3 Постановлением Комитета Российской Федерации по стандартизации, метрологии и сертификации от 14.09.95 № 473 государственный стандарт ГОСТ 26.201.2-94 введен в действие непосредственно в качестве государственного стандарта Российской Федерации с 1 июля 1996 г.

Настоящий стандарт содержит полный аутентичный текст международного стандарта МЭК 640-79 «Система КАМАК. Последовательная магистраль интерфейсной системы»

4 ВЗАМЕН ГОСТ 26.201.2-84

ГОСТ 26.201.2-94

(МЭК 640-79)

МЕЖГОСУДАРСТВЕННЫЙ СТАНДАРТ

СИСТЕМА КАМАК

Последовательная магистраль

интерфейсной системы

САМАС. Serial Highway Interface System

Дата введения 1996-07-01

РАЗДЕЛ 1 ОБЩИЕ ПОЛОЖЕНИЯ

1 Область распространения

Стандарт распространяется на интерфейсную систему, называемую последовательной магистралью КАМАК. Она предназначена для использования в качестве стандартного интерфейса между рядом контрольно-измерительных приборов системы КАМАК, блоками выводов данных, блоками управления, драйверами, оборудованием обработки данных (ЭВМ) и системой коммуникаций.

Последовательная магистраль представляет собой однонаправленную замкнутую цепь для передачи сообщений байтами, к которой подключают контроллер и до 62 крейтов КАМАК в соответствии с ГОСТ 27080 или другие управляемые устройства. Магистраль передает данные и информацию управления либо в виде бит (с одной линией для данных и одной линией для битовых тактовых сигналов), либо в байтовой форме (с использованием восьми линий для данных и линии для байтового тактового сигнала). Синхронизирующая частота может достигать 5 МГц в зависимости от характеристики отдельных систем.

Контролируемые устройства представляют собой крейты КАМАК с последовательными крейт-контроллерами, которые согласуются с определенной структурой сообщений. В данном случае последовательная магистраль (МП) предназначена для дополнения магистрали ветви (МВ) в соответствии с ГОСТ 26.201.1.

Интерфейс MB не рекомендуется в случаях, когда, например, имеются большие расстояния между крейтами или требуется их более простое соединение. Однако для проведения полной операции, включая цикл магистрали крейта (МК), требуется, как правило, больше времени в последовательной магистрали, чем в параллельной магистральной ветви.

Система последовательной магистрали определяется прежде всего форматом сообщений и стандартами сигнала у входа и выхода устройств, соединенных магистралью. Взаимосвязи между устройствами могут осуществляться либо непосредственно с использованием определенных стандартных сигналов, либо с использованием иных сигнальных стандартов и типов модуляции.

Стандарт частично распространяется и на управляемые устройства, соединенные с МП, спроектированные необязательно по стандарту КАМАК или управляемые по командам КАМАК.

Последовательные крейт-контроллеры, полностью соответствующие спецификации, и устройства, согласующиеся с определенной частью полной спецификации, могут сосуществовать на магистрали без дополнительного интерфейса.

1а Нормативные ссылки

В настоящем стандарте использованы ссылки на следующие стандарты:

ГОСТ 27080-93 КАМАК. Модульная система технических средств для обработки данных.

ГОСТ 26.201.1-94 Система КАМАК. Организация многокрейтовых систем. Требования к магистрали истин и крейт-контроллеру КАМАК типа А1.

2 Назначение

Описать и дать характеристику последовательной системы КАМАК. Определить форматы сообщений и стандарты сигналов.

Настоящий стандарт является дополнением к требованиям, изложенным в ГОСТ 27080, его следует использовать совместно с указанной публикацией. Настоящий стандарт не может заменить или модифицировать ГОСТ 27080.

Настоящий стандарт:

- устанавливает обязательные требования;

- определяет рекомендуемые или предпочтительные требования;

- дает примеры допускаемой практики.

Последовательные крейт-контроллеры, приведенные в данном стандарте, не должны быть обязательно взаимозаменяемыми. Однако в приложении А изложены более четко требования к последовательному крейт-контроллеру типа L2, так что блоки, изготовленные различными предприятиями по спецификации приложения А, могут быть взаимозаменяемыми при эксплуатации.

Чтобы соответствовать данному стандарту, оборудование или система должны удовлетворять всем обязательным требованиям, включенным в данный стандарт без приложений. Если оборудование выполнено в виде вставного блока КАМАК, оно должно также удовлетворять обязательным требованиям ГОСТ 27080.

Чтобы соответствовать стандартной спецификации на последовательный крейт-контроллер типа L2, оборудование должно удовлетворять всем обязательным требованиям приложения А.

Чтобы быть совместимым с требованиями данного стандарта, оборудование: необязательно должно удовлетворять всем его требованиям, но при условии, что оно не будет влиять на работу блоков последовательного канала и последовательного крейт-контроллера (включая тип L2), как определено в данном стандарте.

Настоящий стандарт не исключает использования совместного оборудования (в вышеупомянутом смысле), даже если оно полностью не соответствует данному стандарту или не спроектировано по типу вставных блоков КАМАК.

3 Форма выражения требований

Стандарт содержит обязательные требования, рекомендации и примеры допускаемой практики.

Обязательные требования стандарта заключены в «рамку» и обычно включают слово «должны» (must).

Определения рекомендуемой или предпочтительной практики, которой рекомендуется придерживаться, если нет никаких веских причин не следовать ей, включают слово «следует» (should).

Примеры допускаемой практики обычно включает слово «может» (may) и оставляют свободу выбора разработчику или пользователю.

4 Сокращения и обозначения

В стандарте использованы следующие сокращения и условные обозначения:

А «Субадрес» (сигнал МК)*.

БВК (ACL)** Блокировка вспомогательного контроллера

В «Занято» (сигнал МК)*.

БТ (BCL)** Байтовый тактовый сигнал

С «Сброс» (сигнал МК)*.

КЗ (CBY)** Контроллер «занят».

ФТ (DSBY)** Формирование сообщения о требовании обслуживания.

DERR Задержанная ошибка.

ИСТ (DMI)** Инициирование сообщения о требовании обслуживания.

DSQ Задержанный сигнал ответа.

DSX Задержанный ответ принятой команды.

ВП (ERPT)** Внешний повтор.

ERR Бит «Ошибка».

I Сигнал «Запрет» (сигнал МК)*.

L Запрос на внимание (сигнал МК)*.

LAM Сигнал источника запроса в модуле.

МЗБ (LSB)** Наименьший значащий бит.

ИС (MI)** Идентификация типа сообщения.

БЗБ (MSB)** Наибольший значащий бит.

N Номер станции (сигнал МК)*.

NRZL Без возвращения к нулю.

MB (PH)** Магистраль ветви по ГОСТ 26.201.1

Q Ответ, сигнал состояния (сигнал канала крейта).

S Приставка перед обозначениями полей и разрядов последовательного канала.

S1 Стробирующий сигнал (сигнал канала крейта)*.

S2 То же.

SA Разряд субадреса.

ПКК (SCC)** Последовательный крейт-контроллер.

ПКК-L2 (SCC-L2)** Последовательный крейт-контроллер типа L2.

ПМ (SD)** Последовательный драйвер.

SF Бит «Функция».

SGL Обработанный запрос.

SC Разряд адреса крейта.

SGLE Сигнал от сортировщика запросов (ПСЗ) для формирования сообщения о требовании обслуживания.

ПК (SH)** Последовательная магистраль данного стандарта.

ВЗ (SLP)** Выделенный запрос.

SN Бит номера станций.

SQ Бит ответа Q.

БС (SR)** Бит состояния.

ЗТ (STIM)** Запуск таймера.

SW Бит «Запись».

SX Бит «Команда принята».

Т Системный тактовый период.

ЗД (TIMO) Задержка (тайм-аут).

X «Команда принята» (сигнал МК).

Z Сигнал «Пуск» (сигнал МК).

|

Обозначения L, М, N, Р и R (в некоторых случаях с приставкой «СС») оставлены для будущего употребления в соответствии с данным стандартом и не будут использованы, за исключением особых случаев. |

РАЗДЕЛ 2 ПРИНЦИПЫ РАБОТЫ ПОСЛЕДОВАТЕЛЬНОЙ МАГИСТРАЛИ

Данный раздел суммирует основные принципы, которые относятся ко всем устройствам, соединенным с МП. Все другие разделы этого стандарта имеют отношение к основным областям применения, в которых соединенные устройства представляют собой крейты КАМАК с последовательными крейт-контроллерами.

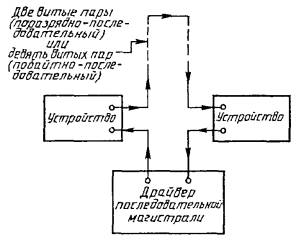

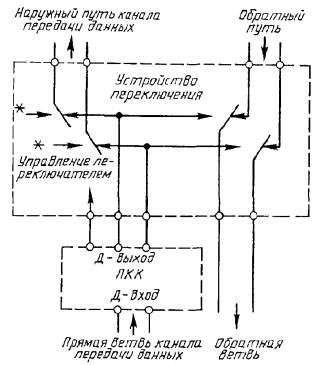

5 Конфигурация

Последовательная магистраль соединяет между собой управляющее устройство (Последовательный драйвер) и до 62 крейтов КАМАК или других управляющих устройств. Постоянно имеется только одно активное основное устройство, но стандарт не исключает систем, в которых могут работать как ведущие более одного устройства. На черт. 1 показана основная конфигурация.

Схема адресации допускает наличие максимум 62 управляемых устройств, адреса которых необязательно должны совпадать с действительной последовательностью устройств по всей магистрали.

Последовательная магистраль образует однонаправленную замкнутую цепь от выхода последовательного драйвера (ПД) через каждое управляемое устройство и обратно к входному порту ПД. При описании условий относительно определенного устройства часто бывает удобно употреблять слово «противоточный» для определения части МП между выходным портом ПД и устройством, и слово «прямоточный» для определения части между устройствами и входным портом ПД.

Конфигурация последовательной магистрали

Черт. 1

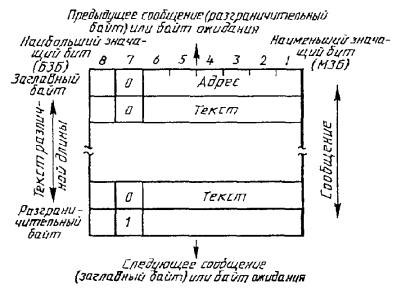

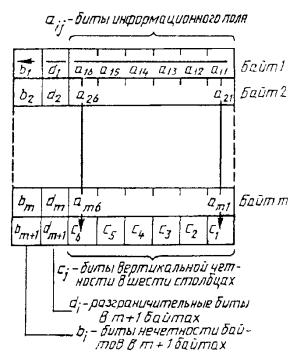

6 Сообщения

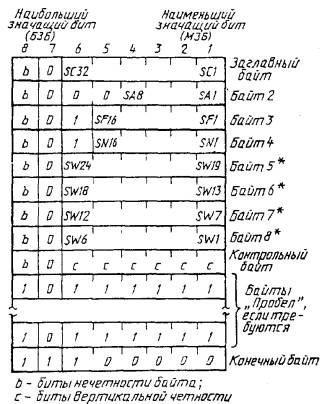

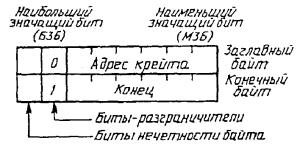

Все сообщения, передаваемые по МП, состоят из последовательности байтов, как показано на черт. 2. Вся информация, содержащаяся в сообщении, содержится в этих байтах.

Восемь разрядов, составляющих байт, обозначены от разряда 1 (наименьший значащий бит) до разряда 8 (наибольший значащий бит). Во всех байтах имеются разряды от 1 до 6, образующие информационное поле байта.

Формат сообщения

Черт. 2

Разряд 7 каждого байта является разграничительным разрядом, который позволяет приемным устройствам распознавать первый и последний байты каждого сообщения.

Разряд 8 используют в качестве контроля четности (с соответствующим значением, чтобы байт содержал нечетное количество разрядов с состоянием логической «1»). Его всегда используют в этом качестве в первом и последнем байтах сообщения и во всех байтах сообщений, связанных с последовательными контроллерами КАМАК.

Каждое сообщение начинается с заглавного байта. Он включает адрес устройства (адрес крейта в случае с последовательным контроллером). В сообщении, поступающем из ПД, заглавный байт содержит адрес позиции-назначения, в сообщении к ПД - адрес источника. Разряд 7 заглавного байта находится в логическом состоянии «0», а разряд 8 содержит признак чет-нечетности «единиц» по всему байту.

Каждое сообщение заканчивается разграничительным байтом, в котором разряд 7 находится в логическом состоянии «1», а разряд 8 содержит признак чет-нечетности «единиц».

Длина и содержание «текста» между заглавным байтом и разграничительным байтом сообщения могут быть выбраны с учетом специфики отдельного устройства. Этот текст необязательно должен быть однородным для всех устройств в системе. В каждом байте между заглавным байтом и разграничительным разряд 7 находится в логическом состоянии «0».

Если имеются какие-либо байты между разграничительным байтом одного сообщения и заглавным байтом следующего, то они также являются разграничительными байтами с разрядом 7 в логическом состоянии «1».

Таким образом, заглавный байт сообщения может быть идентифицирован, так как после одного или более байтов с разрядом 7 в состоянии логической «1» он будет первым байтом с тем же разрядом в состоянии логического «0». Аналогично может быть идентифицирован конечный байт сообщения, так как после одного или более байтов с разрядом 7 в состоянии «0» это первый байт с разрядом 7 в состоянии «1».

Обнаружение ошибок в массиве байтов, составляющих сообщение или часть сообщения, осуществляют сочетанием байтовой четности в разряде 8 каждого байта и комплектом разрядов четности по столбцам в разрядах 1-6 последнего байта массива. Этот «геометрический код обнаружения ошибок» обнаруживает все одно-, двух-, трех-, четырехразрядные ошибки и более. Схема обеспечивает хорошую защиту от групповых ошибок и легко реализуется аппаратным и математическим обеспечением.

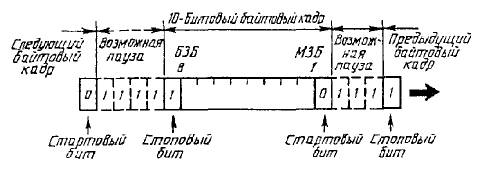

7 Передача байтов

Байты передаются либо в поразрядно-последовательном режиме (с использованием одного информационного сигнала и сопровождающего тактового разрядного сигнала), либо в побайтно-последовательном режиме (с использованием 8 информационных сигналов и сопровождающего байтового тактового сигнала).

В поразрядно-последовательном режиме 8-разрядный байт передается, начиная с наименьшего значащего бита (разряд 1). Ему предшествует старт-бит (логическое состояние «0»), а за ним следует стоп-бит и необязательные биты-паузы (логическое состояние «1»), как показано на черт. 3. Старт-стопные биты образуют байтовый кадр, который позволяет устройствам выделить байтовый тактовый сигнал.

Байтовый кадр для поразрядно-последовательного режима

Черт. 3

В тексте настоящего стандарта комбинация двоичных знаков 8-разрядного байта с наименьшим значащим битом и наибольшим значащим битом представлена последовательностью разрядов (miiiiii1)2. Такой же байт с старт-стопными разрядами представлен последовательностью вида (1, miiiiii1, 0).

Структура сообщения и протокол последовательной магистрали идентичны в двух режимах передачи.

По всей последовательной магистрали байты передаются синхронно с байтовым тактовым сигналом, который сопровождает данные в побайтно-последовательном режиме передачи и выделяется из байтового кадра в поразрядно-последовательном режиме.

В каждом байтовом тактовом периоде каждое устройство принимает и передает один байт, но содержимое (разряды 1-8) принятых и переданных байтов не всегда идентично. Устройства обычно передают содержимое всех принятых байтов, хотя содержимое байта, полученного в одном байтовом периоде, может быть ретранслировано в более позднем байтовом периоде. Устройство может генерировать собственное сообщение посредством прерывания этого процесса ретрансляции. Содержимое необходимого количества байтов генерируется данным устройством, а содержимое соответствующего количества принятых байтов не ретранслируется. Протокол сообщений должен гарантировать, что принятые байты не содержат важной информации. Например, они могут быть байтами «пробел» или байтами «ожидания», как описано в разд. 3.

8 Системные тактовые сигналы

Системные тактовые сигналы с соответствующей частотой следования для передачи бит или байтов генерируются в одной точке системы (обычно у ПД или внутри его) и ретранслируются каждым устройством, соединенным с ПК.

Поэтому частота следования тактовых сигналов равномерна по всей системе. Абсолютная максимальная частота системных тактовых сигналов 5,0 МГц, но работа каналов связи или связанных с ними устройств может требовать более низкой частоты системных тактовых сигналов в определенных системах.

9 Порты последовательной магистрали

Характеристика последовательной магистрали (например, стандарты сигнала, синхронизация, структура сообщения и тип соединителя) определяется по отношению к портам*, через которые канал передачи данных входит и выходит из каждого соединенного с ним устройства.

* «Порт» - включение или отключение от магистрали.

В настоящем стандарте не исключается соединение устройств, выполненных по различным стандартам, или использование различных магистральных связей, применяемых между устройствами.

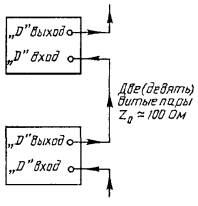

Все устройства, соединенные с магистралью, имеют два порта: один для входа и один для выхода. Эти порты либо соответствуют определенным данным стандартом D-портом, либо относятся к стандартным таким образом, что устройство в принципе могло бы быть соединено с D-портами через соответствующий адаптер.

У каждого D-порта формируемые информационные и тактовые сигналы являются сигналами уравновешенного типа без привязки к нулю (NRZL) и соответствуют стандарту интерфейса для цифровых сигналов с балансированным напряжением (см. разд. 7). Каждый сигнал проводится по отдельной паре линий, генерируется балансным передатчиком и принимается дифференцированным приемником.

У каждого D-порта имеется пара контактов для тактовых сигналов (для передачи с частотой битовых или байтовых тактовых сигналов) плюс восемь пар для сигналов данных (у которых только одна пара используется в поразрядно-последовательном режиме).

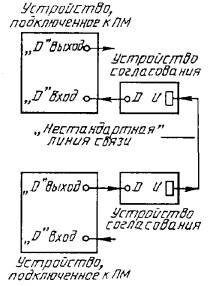

Схему подключения последовательной магистрали можно образовать непосредственным соединением выходного D-порта одного устройства с входным портом D следующего устройства (черт. 4), используя при этом специальный провод в виде витой пары с волновым сопротивлением 100 Ом. Кроме того, любая схема подключения в МП может включать узел связи, в котором стандарты сигнала и технику модуляции выбирают в целях удовлетворения всех специфических требований системы, как показано на черт. 5. В этом случае требуются преобразователи сигналов для преобразования сигналов данных и тактовых сигналов из стандарта D-порта в стандарт иного канала связи и обратно в стандарт D-порта. В контексте этого стандарта любые взаимосвязи, не использующие стандарт D-порта, являются неопределенными и описаны как стандарты U-порта. Хотя сигналы данных и тактовые сигналы передаются по отдельным парам проходов у D-порта, они могут переходить в один однонаправленный провод между U-портами, если, например, использовать соответствующую технику модуляции.

Прямое подключение устройств через D-порты

Черт. 4

Подсоединение устройств через «нестандартные» линии связи

Черт. 5

В пределах системы МП для некоторых частей канала можно использовать стандарты D-порта, в то время как для других - различные стандарты U-порта, при этом, однако, частота тактовых сигналов должна быть везде одинакова. Например, группа вставляемых устройств может иметь прямые взаимосвязи между D-портами, возможно, с одним преобразователем сигнала у входа в группу и другим у выхода из группы.

10 Последовательный драйвер

Последовательный драйвер представляет собой связующее звено между МП (прямо или косвенно) ЭВМ или другим контроллером. Он состоит из передающей части, соединенной с выходным D-портом, и приемной части, соединенной с входным D-портом.

Передающая часть принимает команды и данные из ЭВМ и собирает их в соответствующий формат сообщения с заглавным и разграничительным байтами. Она передает полученный разрядный или байтовый поток в МП, сопровождаемый тактовыми сигналами со скоростью передачи битов или байтов. Она может генерировать код обнаружения ошибок в сообщениях и вставлять байты между последующими сообщениями.

Приемная часть принимает поток бит или байтов из последовательной магистрали вместе с тактовыми сигналами. Она идентифицирует формат байтов сообщения и передает информацию о запросах и состоянии в ЭВМ. Она может проверить код обнаружения ошибок, выполнять процедуры восстановления информации после ошибок и выдавать обратно в канал любые байты между сообщениями.

Последовательный драйвер реагирует на все сообщения, полученные у входного D-порта, в то время как другие устройства реагируют только на те сообщения, которые адресованы им.

Этот стандарт определяет ПД только в виде сигналов, структур сообщения и последовательности сообщений у D-порта. Многие операции, связанные с генерированием и приемом сообщений, могут проводиться либо аппаратными средствами в ПД, либо программными средствами в соответствующей ЭВМ.

Асинхронные последовательные входные схемы имеются в большинстве современных мини-ЭВМ для сопряжения с телетайпами, визуальными устройствами воспроизведения, модемами и т.д. Эти входы могут приводить в действие последовательный канал в поразрядном режиме работы через простой адаптер, что является частным случаем ПД.

11 Расширение использования последовательной магистрали

Каждое управляемое устройство, соединенное с МП, «прозрачно» для сообщений, адресованных другим устройствам независимо от внутренней структуры или длины этих сообщений. МП может таким образом иметь много различных типов совместных устройств при условии, что последние отвечают основным требованиям стандартов сигнала; он также может использовать заглавные и разграничительные байты для установления начала и конца сообщений.

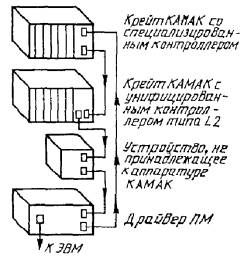

Совместимые устройства, соединенные с МП, могут состоять, например, из элементов, приведенных на черт. 6:

крейты КАМАК с рекомендуемыми крейт-контроллерами типа L2, соответствующими приложению А и использующими структуры сообщений КАМАК, определенные в настоящем стандарте;

крейты КАМАК с другими крейт-контроллерами, соответствующие основной части стандарта и использующие сообщения, являющиеся вариантами или расширениями обычных сообщений КАМАК;

устройства в другом конструктивном исполнении или с другой структурой сообщений.

Подключение устройств

Черт. 6

12 Последовательный крейт-контроллер

При подключении крейта КАМАК к МП последовательный крейт-контроллер (ПКК) используют как связующее звено между ПК и МК. Последовательный крейт-контроллер представляет собой вставной блок КАМАК, занимающий две или более станции в крейте с соединителями для подсоединения к управляющей станции МК и, по крайней мере, к одной рабочей станции. Он имеет соединители передней панели для D-портов.

РАЗДЕЛ 3 СТРУКТУРА СООБЩЕНИЯ ДЛЯ ПОСЛЕДОВАТЕЛЬНЫХ КРЕЙТ-КОНТРОЛЛЕРОВ

Когда крейт КАМАК с последовательным крейт-контроллером (ПКК), образованным по настоящему стандарту, подсоединен к последовательной магистрали (МП), структура сообщения имеет следующие особенности.

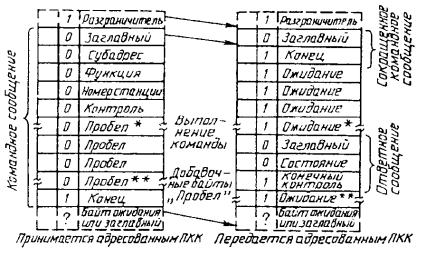

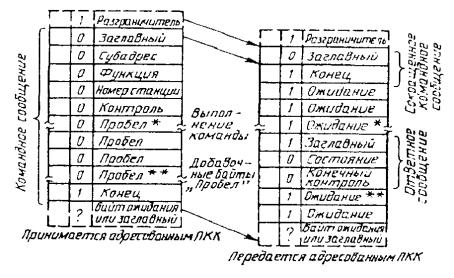

Крейт-контроллеры используют три типа сообщений. «Командные сообщения» генерируют последовательным драйвером и приказывают адресуемому контроллеру выполнить операцию КАМАК. Адресуемый крейт-контроллер может передать в МП сокращенную форму командного сообщения. В ответ на командное сообщение адресуемый крейт-контроллер посылает «Ответное сообщение» в последовательный драйвер. Командное сообщение от драйвера к контроллеру и ответное сообщение от контроллера к драйверу составляют последовательность команда/ответ. Любой последовательный контроллер может генерировать «сообщение о требовании обслуживания», обозначающее, что на МК имеется запрос на обслуживание.

Биты в сообщениях МП отличаются от соответствующих сигналов магистрали крейта префиксом «S». Например, биты SA1-SA8 соответствуют сигналам А1-А8 магистрали крейта.

13 Командные сообщения

Командные сообщения могут быть полные или сокращенные.

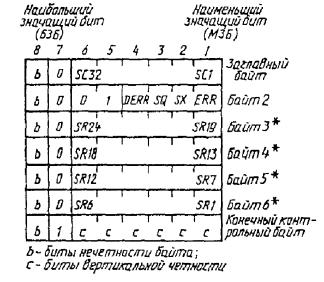

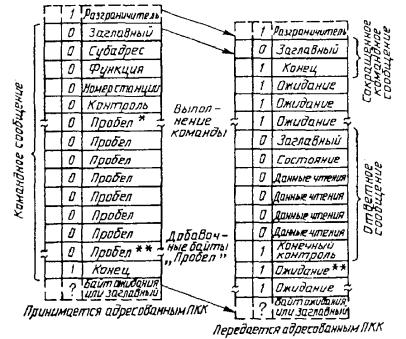

13.1 Полное командное сообщение

|

Полное командное сообщение должно иметь структуру, приведенную на черт. 7, где группа байтов 5-8 включается при выполнении команды записи (SF16 = 1 и SF8 = 0), но опущена в случае команд чтения и управления. Сообщение передастся в виде последовательности байтов, начинающейся с заглавного байта (адрес крейта) и завершающейся конечным байтом. |

Командное сообщение: распределение битов

* Байты 5-8 включаются, если SF16 = 1 и SF8 = 0.

Черт. 7

Полное сообщение в команде состоит из следующих байтов, приведенных на черт. 8: заглавного байта, в котором поле адреса крейта указывает устройство, которому предназначено сообщение; трех байтов, содержащих поля субадреса, функции и номера станции команды КАМАК; четырех байтов, содержащих данные записи из 24 бит, которые опускают, когда они не нужны и контрольный байт (SUM) (см. 17.6), который позволяет адресованному крейту обобщить, проверить и откорректировать команду КАМАК. Далее сообщение продолжают байтом «Пробел» (см. 17.7), представляя возможность ПКК передать ответ, и завершают конечным разграничительным байтом (END) (см. 17.3).

13.2 Сокращенное командное сообщение

Адресованный ПКК должен передавать сокращенную форму командного сообщения, состоящего из заглавного байта и конечного байта (END) (см. черт. 9 и 10).

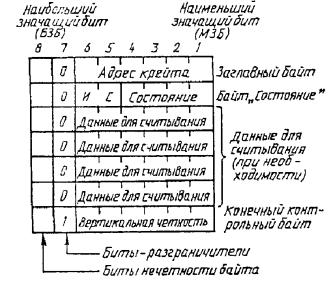

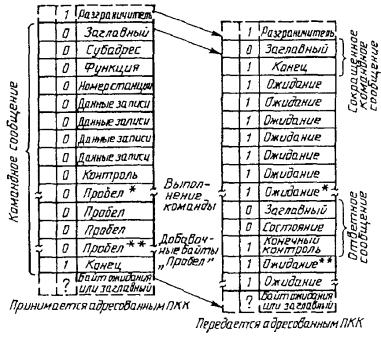

14 Ответное сообщение

|

Ответное сообщение должно иметь структуру, приведенную на черт. 11, в которой группа байтов 3-6 включена в ответ на команду чтения (SF16 = 0 и SF8 = 0), но опущена в ответ на другие команды. Сообщение должно быть передано в виде последовательного ряда байтов, начиная с заглавного байта (адрес крейта) и кончая конечным контрольным байтом (END SUM). |

Командное сообщение: распределение полей

* Зарезервированные биты.

ИС - поле «идентификация типа сообщения».

Черт. 8

Сокращенное командное сообщение: распределение битов

Черт. 9

Сокращенное командное сообщение: распределение полей

Черт. 10

Ответное сообщение: распределение битов

* Байты 3-6 включаются, если SF16 = 0 и SF8 = 0.

Черт. 11

Таким образом, ответное сообщение состоит из следующих байтов (черт. 12): заглавного, в котором поле адреса крейта указывает источник сообщения; байта состояния; четырех байтов, содержащих 24-разрядные данные чтения, которые при ненужности опускают, и разграничительного конечного контрольного байта (END SUM).

15 Сообщение о требовании обслуживания

|

Сообщение на запрос должно иметь структуру, приведенную на черт. 13. Сообщение передают в виде последовательного ряда байтов, начинающегося с заглавного байта (адрес крейта) и кончающегося конечным контрольным байтом. |

Таким образом, сообщение на запрос состоит из следующих байтов (черт. 14); заглавного байта, в котором поле адреса крейта указывает источник сообщения; байта идентифицирующего запрос; конечного контрольного байта (END SUM).

16 Поля сообщений

Информация, содержащаяся в командных, ответных сообщениях и в сообщениях на запрос, разделена на следующие поля:

16.1 Поле адреса крейта (6 бит; SCI-SC32)

Это поле определяет адрес назначения в командных сообщениях и адрес источника на запрос в ответных и запросных сообщениях.

|

Каждый ПКК должен ответить на любой адрес, входящий во множество 018 - 768, и не должен отвечать ни на 00, ни на 778. |

Ответное сообщение: распределение полей

ИС - поле «Идентификации типа сообщения»

Черт. 12

Сообщение о требовании обслуживания: распределение битов

Черт. 13

Сообщение о требовании обслуживания: распределение полей

Черт. 14

Адрес 00 резервирован для использования в последовательном драйвере. При определенных условиях ошибки байт «Пробел» может быть ошибочно идентифицирован как заглавный.

Рекомендуемый байт «Пробел» имеет комбинацию значащих бит, соответствующую адресу 778. Поэтому этот адрес не используют, а применяют адреса крейта 768 (6210).

16.2 Поле номера станции (5 разрядов; SN1 - SN16)

Это поле в командном сообщении определяет номер станции внутри крейта КАМАК (см. 5.1.1 ГОСТ 27080).

Как правило, коды N (1) - N (23) употребляют в качестве адресов модулей в крейте КАМАК. Внутренняя адресация ПКК определяется кодом N (30) (см. разд. 11).

16.3 Поле субадреса (4 разряда; SA1 - SA8)

Это поле в командном сообщении определяет субадрес на выбранной станции в крейте (см. 5.1.2 ГОСТ 27080).

16.4 Поле функции (5 разрядов; SF1 - SF16)

Это поле в командном сообщении определяет операцию, которая должна быть выполнена на выбранной станции и субадресе в крейте (см. 5.1.3 МЭК 516).

Значения SF16 и SF8 в этом поле отличаются в командах чтения, записи и управления, и, следовательно, определяют, включено ли поле данных в командное или ответное сообщение. Длина командных или ответных сообщений, соответствующих различным значениям SF16 и SF8, приведена в табл. 1.

Таблица 1 - Длина цикла команда/ответ

|

Функциональное поле |

Число байтов |

||||

|

F16 |

F8 |

Команда от заглавного байта до разграничительного |

Ответ от заглавного байта до разграничительного |

Цикл команда/ответ |

|

|

Чтение |

0 |

0 |

5 |

7 |

12* |

|

Управление |

0 |

1 |

5 |

3 |

8* |

|

1 |

1 |

||||

|

Запись |

1 |

0 |

9 |

3 |

12* |

|

* Минимальная длина при условии, что заглавный байт ответа передается ПКК, как только получен байт «Пробел», а конечный контрольный байт передается, как только получен конечный байт. |

|||||

16.5 Поле записи данных (24 разряда SW1 - SW24)

Это поле включается в командное сообщение, если SF16 = 1, SF8 = 0. Оно содержит данные, связанные с командой записи.

16.6 Поле чтения (24 разряда; SR1 - SR24)

Это поле включается в ответное сообщение, если поле функций командного сообщения имеет SF16 = 0 и SF8 = 0. Оно содержит данные, запрашиваемые командой чтения.

16.7 Поле идентификации типа сообщения (2 разряда; M1 - М2)

Это поле в командных и ответных сообщениях (2 разряда) и в запросах (только М2) используют для идентификации трех типов сообщений.

|

Значение поля идентификации сообщения должно быть такое, как показано в табл. 2. |

Таблица 2 - Содержание поля идентификации сообщения

|

ИС-поле |

||

|

М2 |

M1 |

|

|

Команда |

0 |

0 |

|

Ответ |

0 |

1 |

|

Запрос |

1 |

- |

Это поле используется последовательным драйвером для различения ответных сообщений и запросов равной длины. Кроме того, его использует ПКК для идентификации командных сообщений в качестве дополнительной гарантии против ложных команд.

16.8 Поле состояния (4 разряда; ERR, SX, SQ, DERR)

Это поле в ответном сообщении показывает, как ПКК ответил на командное сообщение. Разряд ошибки (ERR) указывает, удовлетворителен ли контроль обнаружения ошибки в командном сообщении (см. 63.1).

Разряд задержанной ошибки (DERR) обеспечивает аналогичную информацию о предшествующей команде. В ответ на выполненную команду SQ- и SX-разряды указывают ответ (Q) и состояние принятой команды (X) модуля или контроллера, выбранного командой.

|

Содержимое поле состояния в ответном сообщении должно соответствовать требованиям, изложенным в разд. 46 и 63. |

16.9 Поле местонахождения источника запроса (SGL) (5 разрядов; SGL1 - SGL5).

Это поле сообщения о запросе опознает тип запроса, источник запроса или действие, необходимое по запросу. Оно может формироваться от L-сигналов на магистрали крейта любым процессом выборки, группирования, приоритетного кодирования и т.д., который выполняется крейт-контроллером или отдельным кодирующим устройством сортировки заявок, соединенным с ПКК (см. разд. 14).

Комбинация двоичных знаков (111112) должна использоваться только для указания состояния запроса (см. разд. 14).

17 Форматирующие байты

Задающие формат байты являются частью структуры сообщения, но не содержат информационные поля, как это указано в разд. 16. Они указывают конец каждого сообщения (END и END SUM), обеспечивают элемент контроля качества по столбцу геометрической схемы обнаружения ошибки (SUM и END SUM), сохраняют синхронизацию байтов в пределах сообщений (байты пробел) и между ними (байты ожидания).

Разграничительный байт должен иметь разряд 7 в логическом состоянии «1» и разряд 8 соответствующего значения для сохранения нечетности числа логических «1» в байте.

Все другие байты, не удовлетворяющие этим требованиям, являются неразграничительными байтами. Класс разграничительных байтов включает конечные байты, конечные контрольные байты и байты ожидания.

Разграничительные байты указывают последний байт каждого сообщения и образуют последовательность байтов между сообщениями. Каждое сообщение состоит из ряда неразграничительных байтов, заканчивающегося разграничительным байтом. За ним могут следовать дополнительные разграничительные байты (байты ожидания). Разграничительные байты вполне законно не могут появляться где-нибудь внутри сообщений.

Таким образом, первый байт сообщения (заглавный байт) может быть опознан по контексту как неразграничительный байт, следующий за одним или более разграничительными байтами. Последний байт сообщения опознается по его контексту как первый разграничительный байт, следующий за одним или более неразграничительными байтами.

17.2 Поле контроля четности по столбцам

Контрольные байты и конечные контрольные байты содержат поле с данными контроля четности по столбцам в разрядах 1-6. Это поле обеспечивает контроль четности по столбцам геометрической схемы обнаружения ошибки (см. разд. 61). Каждый разряд поля сохраняет четность числа логических «1» в соответствующей позиции разряда каждого байта от заглавного байта до контрольного байта или конечного контрольного байта включительно.

Содержимое поля эквивалентно сумме по модулю два предшествующих байтов сообщения, исключая разряды 7 и 8 в каждом байте (отсюда термины контрольный и конечный контрольный байты).

Конечный байт - это разграничительный байт, генерированный драйвером в целях завершения полных командных сообщений и крейт-контроллерами в целях завершения сокращенных командных сообщений.

В конечном байте разделительный разряд (разряд 7) находится в логическом состоянии «1», а разряд 8 сохраняет контроль нечетности побайтно.

|

Конечный байт с комбинацией двоичных знаков 111000002, эквивалентный значению 3408, должен быть генерирован последовательным драйвером как последний байт каждого командного сообщения. |

Несмотря на то, что конечный байт имеет такую же комбинацию двоичных знаков, что и байт ожидания (см. 17.4), он отличается расположением в контексте и требованиями, связанными с его ретрансляцией крейт-контроллерами. Конечный байт всегда следует за неразграничительным байтом.

Все неадресованные крейт-контроллеры должны ретранслировать принятые конечные байты без изменений. Адресуемый крейт-контроллер должен либо ретранслировать принятый конечный байт командного сообщения, либо заменить его конечным контрольным байтом (см. 18.4).

17.4 Байт ожидания

Байт ожидания - это разграничительный байт, генерированный последовательным драйвером и адресуемыми крейт-контроллерами. Драйвер может генерировать байты ожидания между последовательными командными сообщениями. Адресуемый крейт-контроллер генерирует байты ожидания в ответ на принятые байты между сокращенным командным сообщением (см. 13.2) и заглавным байтом ответного сообщения, а также, в случае необходимости, между конечным контрольным байтом сообщения и окончанием последовательности команда/ответ. Байт ожидания не имеет информационного поля, но относящийся к нему байтовый тактовый сигнал способствует распространению сообщений по МП. Таким образом, хотя совсем необязательно, чтобы драйвер генерировал байты в интервалах между командными сообщениями, генерация байтов ожидания желательна, так как она способствует распространению командных сообщений и позволяет закончить распространение ответных сообщений в типичном последовательном канале, включающем логические задержки.

|

Любые байты, генерированные последовательным драйвером или последовательным крейт-контроллером, в интервалах между сообщениями должны быть байтами ожидания с комбинацией двоичных знаков 111000002 (3408). |

В этой комбинации байтов разделительный разряд (бит 7) устанавливается в логическое состояние «1», разряд 8 также находится в состоянии «1» для сохранения контроля нечетности по всему байту. Поэтому байт ожидания имеет ту же самую комбинацию двоичных знаков, что и конечный байт (см. 17.3), но отличается по контексту и по условиям его ретрансляции крейт-контроллерами. Байт ожидания всегда следует за другим разграничительным байтом. При определенных условиях, связанных с генерацией запросов, допускается передача крейт-контроллером еще одного байта вместо принятого байта ожидания (см. разд. 5).

Для байта ожидания была установлена особая комбинация двоичных знаков, способствующая процессу синхронизации сообщений (см. 40.3), который обычно имеет место во время генерации драйвером последовательности байтов ожидания. Выбранная комбинация одна из нескольких, имеющих полезное свойство, когда байты ретранслируются в поразрядно-последовательном режиме, а именно: каждый байт, включающий стартовый и столовый биты, имеет только один переход от «0» к «1» и один переход от «1» до «0», способствуя тем самым установлению синхронизации байтов.

17.5 Конечный контрольный байт

Конечный контрольный байт - это разграничительный байт, генерируемый крейт-контроллером для завершения каждого ответного сообщения или запроса.

Поле данных для контроля четности по столбцам (разряды 1-6) сохраняет четность по столбцам по всем байтам между начальным байтом и конечным контрольным байтом включительно.

Разделительный разряд (разряд 7) находится в состоянии логической «1», а разряд 8 сохраняет побайтовый контроль на нечетность всего конечного контрольного байта.

17.6 Контрольный байт

Контрольный байт - неразграничительный байт, генерируемый драйвером в командном сообщении (см. черт. 7 и 8). Поле контроля четности по столбцам (разряды 1-6) этого байта сохраняет четность по столбцам по всем байтам сообщения между заглавным байтом и контрольным байтом включительно. Разделительный разряд (разряд 7) находится в состоянии логического «0», а разряд 8 сохраняет побайтовый контроль на нечетность всего контрольного байта. Адресуемый крейт-контроллер использует контрольный байт при проверке обнаружения геометрической ошибки в командном сообщении перед тем, как решить, нужно ли выполнять команду.

Байт «Пробел» - неразграничительный байт. Последовательность байтов «Пробел», генерируемая драйвером между контрольным и конечными байтами командного сообщения, образует пространство ответа. Адресуемый ПКК генерирует свое ответное сообщение вместо некоторых или всех байтов «Пробел» в пространстве ответа.

|

В байте «Пробел», генерированном последовательным драйвером, разделительный разряд (разряд 7) должен быть в состоянии логического «0», а разряд 8 должен сохранять данные о контроле на нечетность. |

Комбинация двоичных знаков байтов «Пробел», генерированная последовательным драйвером, должна быть 101111112 и эквивалентна 2778.

|

Последовательный крейт-контроллер, которому нужно принять байты «Пробел» в пространстве ответа командного сообщения, должен принять любой неразграничительный байт как замену байту «Пробел». |

Допускаемая замена байтов «Пробел» не требует рекомендуемой комбинации или сохранения нечетности по байту.

РАЗДЕЛ 4 ПОСЛЕДОВАТЕЛЬНОСТЬ СООБЩЕНИЙ КОМАНДА/ОТВЕТ

Этот раздел определяет последовательность входных и выходных байтов, возникающих, когда крейт-контроллер принимает командное сообщение, выполняет чтение, запись или управление по системе КАМАК и передает ответное сообщение. Более подробно некоторые особенности пространства ответа рассматриваются в пределах командного сообщения.

Последовательность сообщений для выполнения операции чтения, записи и управления в поразрядно-последовательном режиме приведена на черт. 15, 17 и 19 соответственно. Соответствующая последовательность сообщений в побайтно-последовательном режиме приведена на черт. 16, 18 и 20. На чертежах показана ситуация, когда ошибки в передаче и буферизация информации в ПКК отсутствует (см. разд. 25).

Последовательности сообщений команда/ответ для операций чтения, записи и управления различают только наличием или отсутствием полей данных. Для этого типа операции последовательности сообщений в поразрядно-последовательном и побайтно-последовательном режимах различаются только относительным сдвигом по времени принятых и переданных байтов в начале и конце последовательности. В поразрядно-последовательном режиме ретрансляция байтов (указанная стрелками на чертежах) обычно включает задержку только на один битовый период, в то время как в побайтно-последовательном режиме допускается задержка на один байтовый период.

Как видно из чертежей, дополнительные байты «Пробел» могут быть добавлены к пространству командного сообщения по двум причинам: имеющиеся байты «Пробел», обозначенные символом «*», дают время для выполнения команды. Минимальное число этих байтов, в принципе, равно нулю, но минимум в один байт может быть более удобным для выполнения операции. Необязательные дополнительные байты «Пробел», обозначенные символом «**», используют в одном способе контролирования длины пространства ответа (см. 23.2). Минимальное количество этих байтов равно нулю.

Последовательность обмена команда/ответ: операция чтения, поразрядно-последовательный режим

* Байты, необходимые для выполнения команды (минимальное число - 0).

** Байты, необходимые для размещения добавочных байтов «пробел» (минимальное число - 0).

Черт. 15

Последовательность обмена команда/ответ: операция чтения, побайтно-последовательный режим

* Байты, необходимые для выполнения команды (минимальное число - 0).

** Байты, необходимые для размещения добавочных байтов «пробел» (минимальное число - 0).

Черт. 16

Последовательность обмена команда/ответ: операция записи, поразрядно-последовательный режим

* Байты, необходимые для выполнения команды (минимальное число - 0).

** Байты, необходимые для размещения добавочных байтов «пробел» (минимальное число - 0).

Черт. 17

Последовательность обмена команда/ответ: операция записи, побайтно-последовательный режим

* Байты, необходимые для выполнения команды (минимальное число - 0).

** Байты, необходимые для размещения добавочных байтов «пробел» (минимальное число - 0).

Черт. 18

Последовательность обмена команда/ответ: операция управления, поразрядно-последовательный режим

* Байты, необходимые для выполнения команды (минимальное число - 0).

** Байты, необходимые для размещения добавочных байтов «пробел» (минимальное число - 0).

Черт. 19

Последовательность обмена команда/ответ: операция управления, побайтно-последовательный режим

* Байты, необходимые для выполнения команды (минимальное число - 0).

** Байты, необходимые для размещения добавочных байтов «пробел» (минимальное число - 0).

Черт. 20

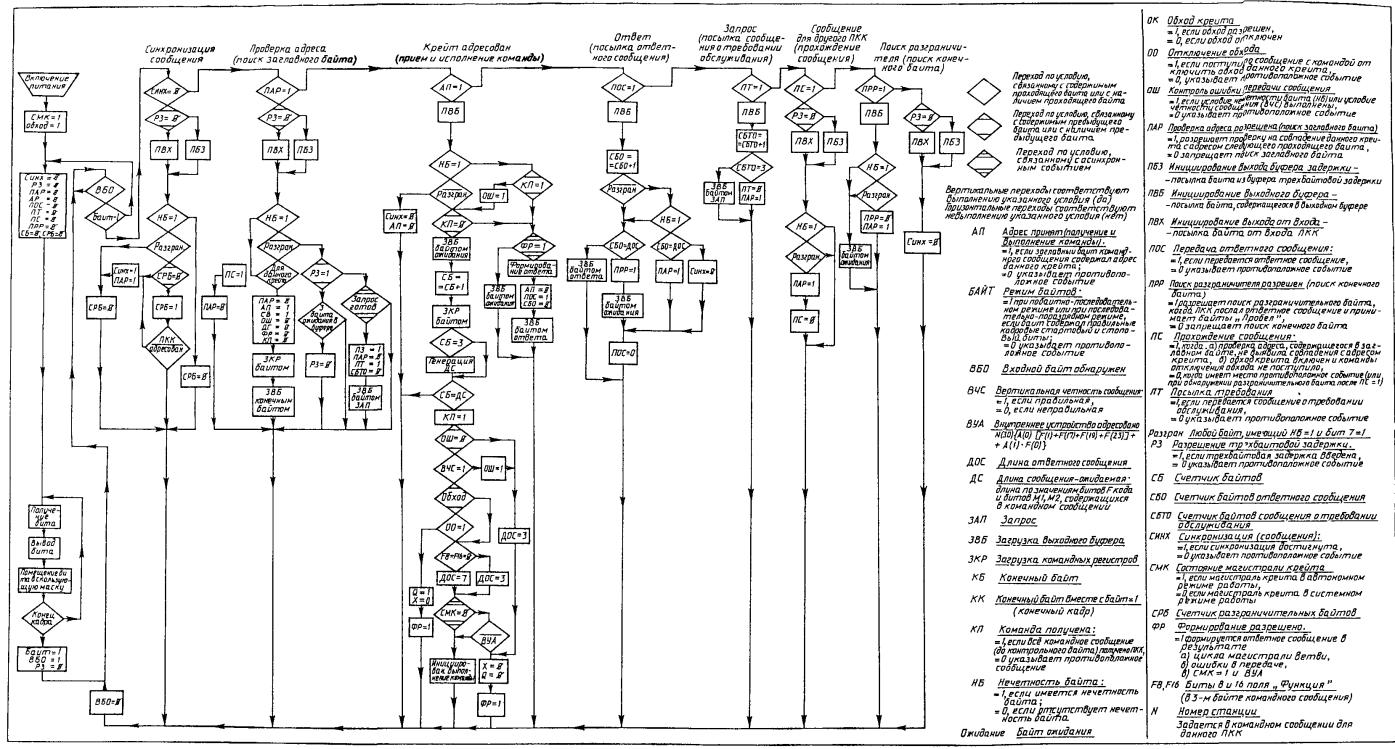

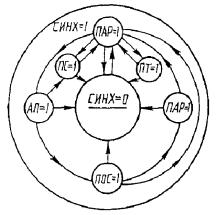

18 Общие требования

Крейт-контроллер обычно поджидает заглавный байт. Последовательный драйвер посылает командное сообщение (см. разд. 13), состоящее из заглавного байта, командного и информационного байтов, контрольного байта, последовательности байтов «Пробел» и конечного байта. Крейт-контроллер опознает заглавный байт, адресованный ему, принимает и контролирует команду и данные, выполняет команду и посылает ответ в периоде пространства и, наконец, заканчивает запись событий, когда он принимает конечный байт.

18.1 Состояние поиска заглавного байта

Эта последовательность предполагает, что крейт-контроллер принял ранее один или более разграничительных байта (конечный или конечный контрольный байт предыдущего сообщения, за которым, возможно, следует один или более байтов ожидания) и ожидает заглавный байт в начале нового сообщения.

|

Когда крейт-контроллер ждет заглавный байт, он должен ретранслировать каждый байт, который он принимает, а также проверять содержимое каждого байта в целях выполнения соответствующего действия, а именно: - если крейт-контроллер принимает разграничительный байт (с разрядом 7-1 и правильной четностью байта), он должен остаться в ожидании заглавного байта и дать разрешение на выдачу своих сообщений о требовании обслуживания; - если крейт-контроллер принимает неразграничительный байт (с разрядом 7-0, верной четностью, а поле адреса крейта соответствует его 6-разрядному адресу), он должен воспринять его как заглавный байт командного сообщения, адресованного ему. Он должен запретить выдачу своих сообщений о требовании обслуживания и приготовиться принять остальную часть командного сообщения; если крейт-контроллер принимает какой-нибудь другой байт, кроме разграничительного или заглавного байта сообщения, адресованного ему, он должен воспринять его как заглавный байт сообщения для (или от) другого контроллера. Он должен запретить выдачу своих сообщений о требовании обслуживания и ретранслировать последующее сообщение без изменений. |

18.2 Состояние приема командного сообщения

При приеме командного сообщения адресуемый крейт-контроллер должен передать сокращенную форму командного сообщения (см. 13.2), состоящего только из заглавного и конечного байта, за которым следует ряд байтов ожидания, необходимых для подготовки им ответного сообщения (см. разд. 14).

|

Адресуемый последовательный крейт-контроллер должен использовать состояние разрядов SF16 и SF8 в поле функции командного сообщения (см. 16.4) для определения, ожидается ли контрольный байт как пятый (если SF16 = 0 и SF8 = 1) или как девятый байт (если SF16 = 1 и SF8 = 0) принимаемого сообщения. Адресуемый крейт-контроллер должен проверить четность по столбцам принятого командного сообщения от заглавного байта до контрольного байта включительно. Он также должен проверить нечетность отдельно по каждому байту. |

Адресуемый крейт-контроллер может проверить, равно ли «00» содержимое поля идентификации типа сообщения (см. 16.7).

18.3 Состояние выполнения команды

|

Адресуемый крейт-контроллер должен выполнять команду и посылать соответствующее ответное сообщение, если удовлетворены следующие условия: а) данные побайтного контроля и контроля четности по столбцам верны; б) данные M1-поля (если это проверено) верны; в) крейт-контроллер находится в режиме работы с магистралью (on-line) (см. 48.1); если он автономен (off-line), или же команда адресуется к его внутренним функциональным узлам; г) крейт-контроллер находится в режиме обхода (см. 48.2) или, если он находится в режиме обхода, то данная команда является командой, сбрасывающей этот режим. В противном случае последовательный крейт-контроллер не должен выполнять команду. |

18.4 Состояние передачи ответа

|

Если адресуемый крейт-контроллер остается в состоянии синхронизации сообщений (и в состоянии синхронизации байта, если таковое требуется) во время цикла команда/ответ, он должен послать ответное сообщение. Если крейт-контроллер выполняет команду, он должен послать ответное сообщение с. форматом, соответствующим коду функции и с содержимым результатов операции. Цикл ответного сообщения не должен начинаться до того, как установлены ответы 0 и X (и данные чтения, если таковые имеются). Если выполнение команды включает операцию на магистрали крейта, передача ответного сообщения не должна начинаться раньше времени t3, приведенного на черт. 9 МЭК 516. Если крейт-контроллер не выполняет команду из-за того, что данные для контроля по четности или проверки M1-поля (см. условия а и б пункта 18.3) неверные, он должен послать трехбайтовое ответное сообщение об ошибке (см. 6.2). Если крейт-контроллер не выполняет команды из-за того, что не соблюдены условия, касающиеся автономного режима работы магистрали крейта или режима обхода (см. условия в и г пункта 18.3), он должен послать ответное сообщение с форматом, соответствующим коду функции и с разрядом SX в состоянии логического «0» для указания, что контроллер не принял команду (см. 63.2). |

Если команда не была выполнена, то можно начать передачу ответного сообщения, как только крейт-контроллер получит контрольный байт.

Для определения видов операций, связанных с сигналами исправления устройства обхода и устройства отключения, инициирование ответного сообщения задержано по отношению к выполнению команды (см. 48.2 и 48.3).

Следом за контрольным байтом последовательный драйвер передает, а крейт-контроллер принимает ряд байтов «Пробел», составляющих пространство ответа. Во многих типичных случаях синхронизации цикла канала крейта и скорости передачи данных последовательной магистрали выполнение команды может быть закончено до приема крейт-контроллером первого байта «Пробел». В этом случае крейт-контроллер может передать заглавный байт ответного сообщения, как только он получит первый байт «Пробел», затем передать байт состояния ответа, как только он получит второй байт «Пробел» и т.д.

|

Каждый байт ответного сообщения должен быть передан адресуемым последовательным крейт-контроллером в ответ на принятый байт. После приема контрольного байта и до посылки заглавного байта ответного сообщения последовательный контроллер должен принять любые неразграничительные байты и передать байты ожидания. Крейт-контроллер должен принять любой полученный неразграничительный байт, пока он передает каждый байт ответного сообщения, а при передаче конечного контрольного байта, крейт-контроллер должен принять любой полученный байт, включая разграничительный байт. Если адресуемый крейт-контроллер получает разграничительный байт после того, как он опознал заглавный байт командного сообщения, и до передачи конечного контрольного байта ответного сообщения, он должен выйти из цикла обмена команда/ответ и перейти в состояние потери синхронизации сообщения (см. 40.2). |

В следующих трех подразделах описывается, что крейт-контроллер начинает генерировать ответное сообщение, как правило, когда получает первый байт «Пробел», и что он генерирует конечный контрольный байт, как только он получает конечный байт командного сообщения. В разд. 23 описаны другие допустимые условия, при которых крейт-контроллер принимает байты Пробел» до того, как он закончит выполнение команды в момент передачи и после передачи конечного контрольного байта.

19 Операция чтения

Последовательность байтов, передаваемых последовательным драйвером и крейт-контроллером, приведена на черт. 15 и 16 для поразрядно-последовательного и побайтно-последовательного режимов соответственно. Командное сообщение не включает поле записи данных. Ответное сообщение включает поле 24-разрядной информации чтения.

В поле функции командного сообщения разряды SF16 = 0 и SF8 = 0 обозначают операции чтения. Поэтому крейт-контроллер находит контрольный байт как пятый байт в полученном сообщении и выполняет контроль четности по столбцам по первым пяти байтам сообщения.

20 Операция записи

Последовательность байтов, передаваемых последовательным драйвером и крейт-контроллером, приведена на черт. 17 и 18 для поразрядно-последовательного и побайтно-последовательного режимов соответственно. Командное сообщение включает поле 24-разрядной информации записи. Ответное сообщение не включает поле данных чтения.

В поле функции командного сообщения разряды SF16 = 1 и SF8 = 0 обозначают операции записи. Поэтому крейт-контроллер находит контрольный байт как девятый байт полученного сообщения и выполняет контроль четности по столбцам в первых девяти байтах сообщения.

21 Операция управления

Последовательность байтов, передаваемых последовательным драйвером и крейт-контроллером, приведена на черт. 19 и 20 для поразрядно-последовательного и побайтно-последовательного режимов соответственно. Ни командное, ни ответное сообщения поле данных не включает.

В поле функции командного сообщения разряд SF8 = 1 обозначает операцию управления (ни чтение, ни запись), и поэтому крейт-контроллер ждет контрольный байт как пятый байт в полученном сообщении и выполняет контроль четности по столбцам в первых пяти байтах сообщения.

22 Сокращенное командное сообщение

Адресуемый крейт-контроллер должен передавать сокращенное командное сообщение в ответ на полученное командное сообщение, состоящее только из заглавного байта (содержащего поле адреса крейта) и конечного байта.

Такая практика отражена в последовательности команда/ответ, приведенной на черт. 15-20, и она является обязательным свойством крейт-контроллера типа L2 (см. приложение А, пункт A3.2). Она рекомендована для всех других крейт-контроллеров по следующим причинам. Только один крейт-контроллер может реагировать на командное сообщение, даже если, например, тот же адрес крейта предназначен более чем одному крейту. Последовательный ряд разграничительных байтов, следующий за сокращенным командным сообщением, дает возможность указать начало ответного сообщения, а также обеспечивает возможность для прямоточных (прозрачных) крейт-контроллеров генерировать запросы (см. 24) и восстанавливать синхронизм байтов (см. 41.3).

Однако в некоторых областях применения требуется, чтобы адресуемый крейт-контроллер ретранслировал командное сообщение до (и включительно) контрольного байта. В этих случаях необходимо предусмотреть соответствующие крейт-контроллеры и последовательные драйверы, но они вполне могут сосуществовать на одном и том же последовательном канале с другими контроллерами, которые генерируют рекомендуемое сокращенное командное сообщение.

Если последовательный крейт-контроллер не передает сокращенную форму командного сообщения, то он должен передать по крайней мере один разграничительный байт в ответ на полученный байт непосредственно перед передачей заглавного байта ответного сообщения.

23 Пространство ответа

Этот раздел охватывает некоторые дополнительные аспекты байтов «Пробел», генерированных последовательным драйвером во время передачи командного сообщения, которые частично или полностью заменяются ответным сообщением от адресуемого крейт-контроллера.

23.1 Завершение цикла операций магистрали крейта

Если период байта длинный по сравнению со временем выполнения команды, адресуемый крейт-контроллер готов послать ответ до того, как он получит первый байт «Пробел». При этих условиях первый байт ответного сообщения может быть передан крейт-контроллером вместо первого байта «Пробел».

В противном случае крейт-контроллер принимает один или более байтов «Пробел» перед тем, как он посылает ответ, и количество дополнительных байтов «Пробел», обозначенных знаком «*» на черт. 15-20, не равно нулю. Крейт-контроллер передает байты ожиданий вместо полученных байтов «Пробел», пока он не выполнит команду. Затем он передает первый байт ответного сообщения вместо следующего байта «Пробел».

23.2 Окончание цикла команда/ответ

В одном режиме последовательный драйвер продолжает генерировать дополнительные байты «Пробел» до тех пор, пока он не получит ответного сообщения. Затем он генерирует конечный байт для окончания цикла. Этот режим обладает таким преимуществом, что он устраняет необходимость контроля со стороны последовательного драйвера точного количества байтов «Пробел». Его недостатком является то, что он снижает возможность генерировать запросы от адресуемого крейт-контроллера; во избежание блокировки требуются меры предосторожности, если команда адресуется несуществующему крейту. Количество дополнительных байтов «Пробел», обозначенных знаком «**» на черт. 15-20, не равно нулю, и крейт-контроллер передает байты ожидания вместо полученных байтов «Пробел».

В другом из возможных режимов последовательный драйвер генерирует расчетное число байтов «Пробел», а затем заканчивает цикл посылкой конечного байта. Он продолжает генерировать байты ожидания, пока не получит ответного сообщения. В этом режиме имеется немного дополнительных байтов «Пробел» или совсем нет ни одного.

Оба режима завершения цикла команда/ответ приводят к простому восстановлению после ошибок (разд. 64), так как каждый цикл завершается до того, как начат следующий.

Возможен режим соответствующий высокой производительности с низким коэффициентом ошибки, когда последовательный драйвер не ждет получения ответа на командное сообщение, прежде чем начнет генерировать следующий. В этом режиме последовательный драйвер генерирует точный минимум байтов «Пробел», в результате чего адресуемый крейт-контроллер генерирует конечный контрольный байт ответного сообщения, когда он получает конечный байт командного сообщения. В условиях, когда ошибок нет, последовательный драйвер, работая в этом режиме, передает последовательность командных сообщений и принимает соответствующую последовательность ответных сообщений в том же относительном порядке, но, возможно, значительно позже и со вставленными запросами. В данном режиме нельзя полагаться на повторное чтение в процессе восстановления от ошибок передачи.

23.3. Длина пространства для ответа

|

Последовательный драйвер должен включить внутрь командного сообщения достаточно байтов «Пробел», чтобы крейт-контроллер мог успеть выполнить команду и передать ответное сообщение. |

Ниже приводится простая формула определения длины пространства для ответа. Эта формула относится к рекомендуемому режиму работы, в котором адресуемый крейт-контроллер передает сокращенную форму командного сообщения (см. 13.2). Она также учитывает наихудший режим, при котором крейт-контроллер завершает полный цикл операций в канале каркаса перед посылкой заглавного байта ответного сообщения. Верхняя оценка S необходимого числа байтов «Пробел» в командном сообщении определяется формулой

S = Nраб + Nотв + 1,

где Nраб и Nотв - число байтов «Пробел», необходимых для выполнения команды и передачи ответного сообщения соответственно, причем Nраб - наименьшее целое число, большее Траб / Тбайт, где Траб - максимальное время цикла магистрали крейта для данного крейт-контроллера, a Tбайт - минимальный байтовый период определенной системы последовательной магистрали; Nотв - два байта для команд записи и управления и шесть байтов для команд чтения.

Детально проанализировав временное соотношение между периодом получаемых байтов и длительностью операций магистрали крейта в определенном крейт-контроллере, можно вполне работать с более низким значением S, чем указано в формуле. Например, если байтовый период Тбайт очень длинный по сравнению со временем операции магистрали крейта Tраб, значение Nраб может быть уменьшено путем передачи ответного сообщения до того, как будет завершен полный цикл операции (см. 18.4). В последнем случае необходимо гарантировать, что если две следующие друг за другом команды записи или управления адресуются одному и тому же крейт-контроллеру, число байтов между контрольным байтом одной команды и байтом подадреса следующей команды достаточно для удержания командных сигналов магистрали крейта на всем протяжении цикла операций.

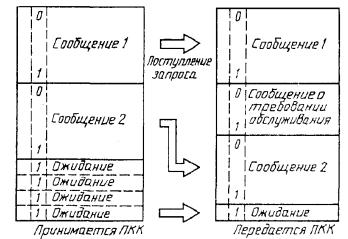

РАЗДЕЛ 5 ГЕНЕРИРОВАНИЕ СООБЩЕНИЯ О ТРЕБОВАНИИ ОБСЛУЖИВАНИЯ

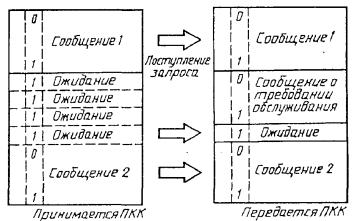

Формат сообщения определен в разд. 15. Любой ПКК может передать запрос в ответ на L-сигнал на магистрали крейта. Он вставляет его между двумя любыми сообщениями, входящими в поступающую в ПКК последовательность сообщений МП.

Генерирование сообщений о запросе управляется разрядами регистра состояния ПКК (см. разд. 47), а также разделительными разрядами байтов, принятых ПКК. Каждый байт с разделительным разрядом в состоянии логической «1» разрешает инициирование запросов. Поэтому ПКК не может генерировать запрос в момент, когда он принимает командное сообщение, адресованное ему, или когда он ретранслирует либо командное сообщение, адресованное другому крейту, либо ответное сообщение или запрос, генерируемые предыдущим крейтом.

Разграничительный байт, который разрешает ПКК начать генерирование трехбайтного сообщения о запросе на обслуживание, может предшествовать разграничительным байтам нового сообщения. Поэтому в ПКК требуется буферная память, чтобы сохранить байты, поступающие в момент передачи запроса.

Если ПКК, адресуемый командным сообщением, предпочитает передать сокращенное командное сообщение (см. 13.2), то наблюдаются различия в процессе генерирования запроса в крейтах с потоком данных в обратном и прямом направлении по отношению к адресуемому крейту. Генерирование запросов запрещено в крейтах с потоком данных в обратном направлении в период полной продолжительности цикла команда/ответ, от заглавного байта до конечного командного сообщения. В крейтах по ходу потока данных генерирование запросов запрещается в момент передачи двухбайтного сокращенного командного сообщения. Конечный байт данного сообщения и следующие байты ожидания разрешают генерирование запроса в интервале между сокращенным командным сообщением и ответным сообщением.

Генерирование запросов опять запрещено заглавным байтом ответного сообщения и разрешено конечным контрольным байтом данного сообщения. На черт. 21 приведена типичная последовательность сообщений, включающая запросы. Запрос здесь генерируется в ПКК1 сразу после того, как передано командное сообщение в ПКК2. Собственный ответ ПКК2 и его сообщение о запросе генерируется им сразу, так что сообщение из ПКК2 вставляется перед запросом от ПКК1 и задерживает его. Сообщение о запросе ПКК3 генерируется им в интервале между сокращенным командным сообщением из ПКК2.

Пример последовательности сообщений, включающий сообщения о требованиях обслуживания

Черт. 21

Примечания

1 Задержки распространения сигналов считают равными нулю.

2 Заштрихованные области указывают, когда возможен запрос от ПКК и его ответ на команду (сокращенное сообщение).

3 Запрос от ПКК1 задерживается на 3 байта в ПКК3.

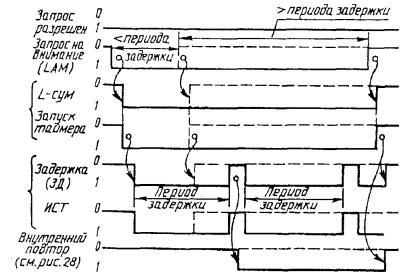

24 Управление инициированием сообщения о запросе

|

Следующие условия должны быть удовлетворены, прежде чем ПКК инициирует генерирование сообщения о запросе: а) генерирование запроса разрешено соответствующим разрядом регистра состояния ПКК (см. 47.1); б) присутствует такой запрос на обслуживание, который либо появился, как только было передано ПКК последнее сообщение о запросе, либо уже присутствовал, когда ПКК переключался в состояние разрешения запроса; в) ПКК способен принять три поступающих байта с одновременным генерированием сообщения о запросе (см. разд. 25); г) предыдущий байт, переданный в выходной порт, был разграничительный байт (см. 17.1). |

ПКК с соединителем SGL-шифратора (см. разд. 53) должен интерпретировать условие б, находится ли сигнал инициирования сообщения о запросе (ИСЗ) в состоянии логической «1» и переключился ли он из состояния логического «0» в логическую «1», когда ПКК компоновал и передавал последнее сообщение о запросе.

25 Буфер задержки

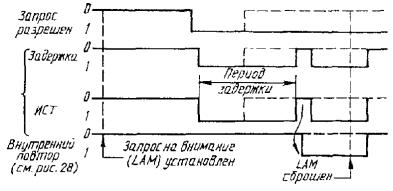

ПКК не разрешено передавать большее количество байтов, чем он получает (см. разд. 35). Поэтому, когда ПКК генерирует трехбайтное сообщение о запросе, он должен удалить три байта ожидания из потока, проходящего вдоль МП. Если поток байтов в определенное время содержит три байта ожидания, каждый байт запроса сразу заменяет один байт ожидания. В противном случае ПКК передает запрос и затем удаляет три байта ожидания, которые появляются позже в байтовом потоке. Это значит, что байтовый поток, проходящий через ПКК, должен быть задержан на время периода до трех байтовых периодов (см. черт. 22).

Генерирование сообщения о требовании обслуживания

а) Сообщение о требовании обслуживания (запрос) прямо замещает байты ожидания

б) Сообщение о требовании обслуживания (запрос) задерживает приходящее сообщение

Черт. 22

В момент, когда ПКК вырабатывает трехбайтовое сообщение о запросе, он должен продолжать принимать байты из МП в свой входной порт. Сообщение о запросе должно вытеснить три байта ожидания из байтового потока, проходящего через ПКК, а все другие байты должны быть переданы в правильной последовательности после того, как передано сообщение о запросе.

Для того, чтобы удовлетворить эти требования, любой ПКК, способный генерировать трехбайтные запросы, должен задержать байтовый поток на соответствующее количество байтовых периодов. Эта задержка не должна быть меньше фактического количества принятых байтов, исключая байты ожидания, в течение времени передачи запроса. Байтовый поток МП должен быть задержан, когда ПКК начинает передавать сообщение о запросе, и должен задерживаться до тех пор, пока все три байта ожидания не будут изъяты из байтового потока МП (при условии, что не произойдет потеря байтового синхронизма (разд. 42). Временная задержка должна включаться и выключаться между сообщениями синхронно с байтовыми и тактовыми сигналами.

Данное требование можно удовлетворить с помощью трехбайтового буфера задержки. Когда ПКК начинает генерировать запрос, поступающие байты задерживаются при прохождении в этом буфере. Рекомендуемый ПКК - L2, описанный в приложении А, пункт А1, включает фиксированную трехбайтовую задержку независимо от содержимого байтового потока. Другой вариант, более сложный, но обеспечивающий лучшую работу системы, заключается в том, что ПКК, передающий сообщение о запросе, включает блок однобайтовой задержки каждый раз, когда он принимает не байт ожидания.

После генерирования трехбайтового запроса ПКК продолжает направлять поступающий байтовый поток через буфер задержки до тех пор, пока он не будет способен удалить три байта ожидания из байтового потока. Затем буфер задержки отключается от линии прохождения последовательности сообщений МП.

Рекомендуемый ПКК-L2, описанный в приложении А, п. А1, включает фиксированную задержку из трех байтов, когда буфер заполнится тремя последовательными байтами ожидания (предшествующий контрольный или конечный контрольный байт прошел через буфер). В третьем допустимом варианте, более сложном, но обеспечивающем лучшую работу, ПКК включает один байтовый блок задержки каждый раз, когда принят байт ожидания (различая настоящий байт ожидания и любой предыдущий конечный байт).

После того, как ПКК генерирует запрос, он не может инициировать другой запрос до тех пор, пока он не получит соответствующее количество байтов ожидания, которые отключают буфер задержки (см. условие в) в разд. 24).

Когда ПКК работает в поразрядно-последовательном режиме и теряет байтовую синхронизацию, задержка, связанная с генерированием запроса, должна быть полностью устранена из последовательности сообщений, которая принимается и ретранслируется ПКК в виде потока байтов (см. разд. 42).

Для более подробной информации, касающейся средств разрешения и запрещения формирования сообщения о запросе и способе проверки состояния запроса (см. разд. 47). Что касается информации о кодировании поля, содержащего данные о местонахождении источника запроса, и о необслуженных запросах (см. разд. 14).

26 Идентификация запросов

Начальный байт запроса указывает крейт, в котором появился запрос. Пятиразрядное SGL-поле во втором байте сообщения может быть использовано для более подробного опознания запроса, например, с помощью кода, обозначающего либо позицию, с которой исходил L-сигнал, либо действие, требующееся по запросу.

Эта информация может быть дополнена командой чтения сообщения о запросе. Каждый разряд слова, считанного этой командой, обозначает состояние соответствующей L-линии магистрали крейта (см. п. 44.1).

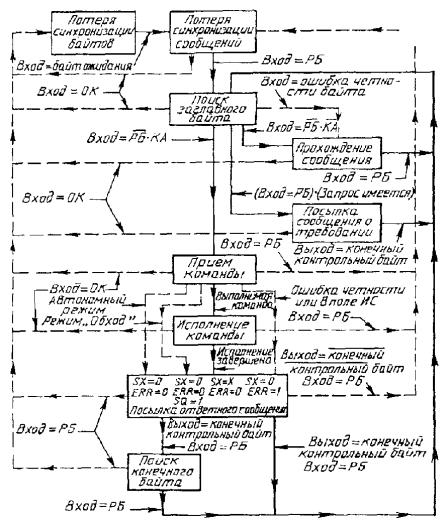

РАЗДЕЛ 6 ИДЕНТИФИКАЦИЯ СООБЩЕНИЙ

При нормальном режиме сообщения в МП состоят из полных командных сообщений (с полем данных записи или без него), сокращенных командных сообщений, ответных сообщений (с полем данных чтения или без него) и сообщений о запросе. При наличии ошибок могут иметь место различные формы неполных и ложных сообщений, вызванных, например, потерей синхронизации, отказами в работе или искажением байтов ожидания. Этот раздел суммирует информацию для ПКК и последовательного драйвера (ПД), для целей различения этих сообщений и опознания байта, содержащего поле с данными для контроля четности по столбцам.

Три основные составляющие этой информации, имеющиеся у ПКК или ПД, - это поле идентификации сообщения (ИС), поле функции (ПФ) и длина сообщения. ИС-поле (см. 16.7) обеспечивает основные способы различения ответного сообщения, запроса и полного командного сообщения. Длина сообщения (количество байтов от начального байта до первого разграничительного байта) обеспечивает способ различения полного и сокращенного командных сообщений, а также ответных сообщений с полем данных и без него. ФС-поле полного командного сообщения различает командные сообщения с полем данных и без него. ПД может также использовать информацию о типах сообщений, ожидаемых на входе в ответ на различные условия, существующие на выходе. Например, когда отсутствует последовательность команда/ответ, ПД должен получить только сообщения о запросе. При наличии последовательности команда/ответ адресные поля крейта любого командного или ответного сообщения должны соответствовать полям переданных командных сообщений.

27 Полное командное сообщение (минимальная длина 8 байтов, ИС = 00)

При нормальных условиях полные командные сообщения принимаются только ПКК (если адресованный ПКК сокращает командное сообщение, как это рекомендовано в п. 23.2), но при наличии ошибок полные командные сообщения могут быть также приняты ПД (например, адресное поле крейта не опознается ни одним ПКК в системе).

По многим причинам адекватная идентификация полных командных сообщений может быть осуществлена у ПКК путем сравнения поля адреса данного сообщения с адресом данного ПКК. Если поле адреса крейта полученного сообщения соответствует адресу ПКК, это сообщение обычно является полным командным сообщением. Другие сообщения могли бы ошибочно удовлетворить это условие, но должны быть в конце концов отвергнуты проверкой поля с данными для контроля четности по столбцам или по длине сообщения. В качестве дополнительного предостережения ПКК может проверить, равно ли содержимое ИС-поля во втором байте 00 (рекомендуемый ПКК-2, описанный в приложении А, п. А1, не проверяет ИС-поле).

Внутри ПКК позиция контрольного байта определяется анализом ПФ: если (![]() 16 + ПФ8) = 1, что указывает на команды чтения или упражнения, поле с данными для контроля четности по столбцам находится в пятом

байте. Если ПФ16 ·

16 + ПФ8) = 1, что указывает на команды чтения или упражнения, поле с данными для контроля четности по столбцам находится в пятом

байте. Если ПФ16 · ![]() 8 = 1, что указывает на команду записи, поле с данными для контроля четности по столбцам находится в девятом байте.

8 = 1, что указывает на команду записи, поле с данными для контроля четности по столбцам находится в девятом байте.

В ПД это сообщение может быть отлично от сокращенного сообщения по его длине (более двух байтов) и от всех других сообщений по его ИС-полю. Поле с данными для контроля четности по столбцам несокращенного командного сообщения, как правило, неуместно в ПД, но могло бы быть идентифицировано, исходя из ПФ.

28 Сокращенное командное сообщение (длина 2 байта, ИС-поля нет)

ПКК не может получить сокращенное командное сообщение, адресованное ему, при правильной работе системы.

Если это происходит по ошибке, длина сообщения вынуждает ПКК отклонить сообщение (по второму разграничительному байту). В ПД это сообщение может быть идентифицировано только своей длиной. Эта идентификация может быть поддержана сравнением полей адреса крейта полученного сообщения и переданного командного сообщения. В сокращенном командном сообщении нет поля с данными контроля четности по столбцам.

29 Ответное сообщение (длина 3 или 7 байтов, ИС = 01)

При правильной работе системы ПКК не может получить ответное сообщение, поле адреса крейта которого соответствует данному ПКК. Если это происходит по ошибке, ПКК обрабатывает его как командное сообщение и в конце концов отклоняет его по проверке поля с данными контроля четности по столбцам, по длине сообщения или по анализу (если выполнена эта проверка) ИС-поля.

В ПД ответное сообщение без поля с данными чтения имеет ту же длину, что и сообщение о запросе, от которого оно может отличаться только ИС-полем. Ответные сообщения с полями данных или без них могут отличаться только длиной сообщения. Поэтому конечный контрольный байт, содержащий поле с данными контроля четности по столбцам, может быть идентифицирован только как первый разграничительный байт в сообщении.

30 Сообщение о требовании обслуживания (длина 3 байта, ИС = 0 -)

При правильной работе системы ПКК не может получать запрос, поле адреса крейта которого соответствует адресу данного ПКК. Если это происходит ошибочно, ПКК будет обрабатывать его как командное сообщение и в конце концов отклонить его либо по контролю поля с данными для контроля четности по столбцам, либо по длине сообщения, или по анализу (если выполнена проверка) ИС-поля.

В ПД сообщение о запросе может быть выделено по ИС-полю. Оно имеет ту же самую длину сообщения, что и ответное сообщение без поля данных. Конечный контрольный байт, содержащий поле с данными для контроля четности по столбцам, может быть идентифицирован как первый разграничительный байт или как третий байт сообщения.

РАЗДЕЛ 7 D-ПОРТЫ ПОСЛЕДОВАТЕЛЬНОЙ МАГИСТРАЛИ

|

Все последовательные крейт-контроллеры и последовательные драйверы должны иметь входные и выходные соединители D-портов и должны осуществлять через эти соединители либо поразрядно-последовательный, либо побайтно-последовательный режимы или оба режима. Любой ПКК, который осуществляет оба режима: поразрядно-последовательный и побайтно-последовательный, должен иметь средства выбора необходимого режима. |

Этот выбор режима может быть осуществлен внутрисхемно в ПКК. Он не должен быть реализован управлением и индикацией с передней панели ПКК.

ПКК или ПД также может иметь дополнительные порты других стандартов (U-порты), если они не исключены по каким-то особым причинам, как в случае с ПКК типа L2.

Через соединители D-порта передают тактовые сигналы и сигналы информации по отдельным парам проводов, используя сигналы вида без возврата к нулю. Через них также передают выходные управляющие сигналы для внешних устройств отключения и обхода (разд. 59).

31 Соединители D-порта

31.1 Конструктивное исполнение

|

Все входные соединители D-порта должны представлять собой 25-контактные штыревые соединители. Все выходные соединители D-портов должны представлять собой 25-контактные гнездовые соединители. |

|

Соединители D-порта должны иметь фиксаторы с винтовым запором (элементы фиксации). |

Расположение соединителей D-порта на передней панели ПКК установлено в разд. 51.

|

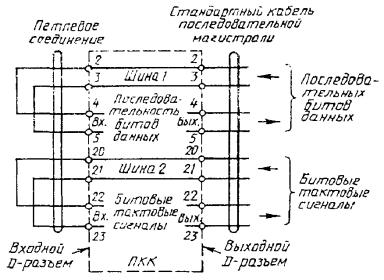

Назначение контактов соединителей D-порта приведено в табл. 3. |

Контакты 22 и 23 используют для битового тактового сигнала в поразрядно-последовательном режиме и для байтового тактового сигнала в побайтно-последовательном режиме.

Контакты 4 и 5 используют для последовательного потока битов в поразрядно-последовательном режиме или для наименьшего бита в побайтно-последовательном режиме.

Семь пар контактов, от контактов 6 и 7 до контактов 18 и 19, используют только в побайтно-последовательном режиме для байтовых разрядов от 2 до 8.

Таблица 3 - Назначение контактов D-соединителей

|

Входной D-соединитель |

Контакт |

Выходной D-соединитель |

|

Общий (Земля) |

1 |

Общий (Земля) |

|

Шина 1 (Свободное использование) |

2 3 |

Шина 1 (Свободное использование) |

|

Бит - последовательные данные или наименьший значащий бит байт-последовательных данных вх |

4 5 |

Бит - последовательные данные или наименьший значащий бит байт-последовательных данных вых |

|

Бит 2 байт-последовательных данных вх |

6 7 |

Бит 2 байт-последовательных данных вых |

|

Бит 3 байт-последовательных данных вх |

8 9 |

Бит 3 байт-последовательных данных вых |

|

Бит 4 байт-последовательных данных вх |

10 11 |

Бит 4 байт-последовательных данных вых |

|

Бит 5 байт-последовательных данных вх |

12 13 |

Бит 5 байт-последовательных данных вых |

|

Бит 6 байт-последовательных данных вх |

14 15 |

Бит 6 байт-последовательных данных вых |

|

Бит 7 байт-последовательных данных вх |

16 17 |

Бит 7 байт-последовательных данных вых |

|

Наибольший значащий бит байт-последовательных данных вх |

18 19 |

Наибольший значащий бит байт-последовательных данных вых |

|

Шина 2 (Свободное использование) |

20 21 |

Шина 2 (Свободное использование) |

|

Битовые (байтовые тактовые сигналы) вх |

22 23 |

Битовые (байтовые тактовые сигналы) вых |

|

Управление устройством обхода |

24 |

Управление устройством обхода |

|

Резервируется для сигнала управления |

25 |

Управление устройством отключения |

|

Примечание.

Каждая балансная входная или выходная линия занимает одну пару контактов. Контакты с четным номером передают «Сигнал». Контакты с нечетным

номером передают « |

||

Контакт 24 входного D-порта соединен с соответствующим контактом выходного D-порта, а также с источником сигнала управления устройством обхода внутри ПКК.

Контакт 25 выходного D-порта соединен с источником сигнала управления устройством аварийного отключения внутри ПКК. Контакт 25 входного D-порта резервирован для использования третьим сигналом управления в случае необходимости.

Контакты 2 и 3 предназначены в качестве шины 1, а контакты 20 и 21 - в качестве шины 2. Эти контакты на входном соединителе D-порта ПКК соединены непосредственно с соответствующими контактами на выходном соединителе D-порта. Шины 1 и 2 представляют собой свободные соединения без определенной функции или направления передачи сигнала.

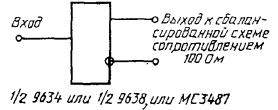

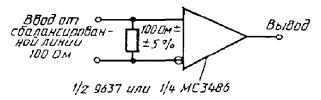

В качестве примера использования контактов шин 1 и 2 может служить черт. 23, изображающий ПКК в поразрядно-последовательном режиме, который может быть соединен с МП только одним 25-жильным кабелем, соединенным с выходным D-портом. Шины 1 и 2 используют здесь для передачи данных в поразрядно-последовательном режиме и битовых тактовых сигналов в ПКК. Перемычки у входного D-порта ПКК соединяют шину 1 с входными данными и шину 2 с входным тактовым сигналом. Цепь, идущая к последовательному драйверу, замыкается обычным путем, через выходной D-порт.

Пример использования контактов шин 1 и 2 D-соединителей

Черт. 23

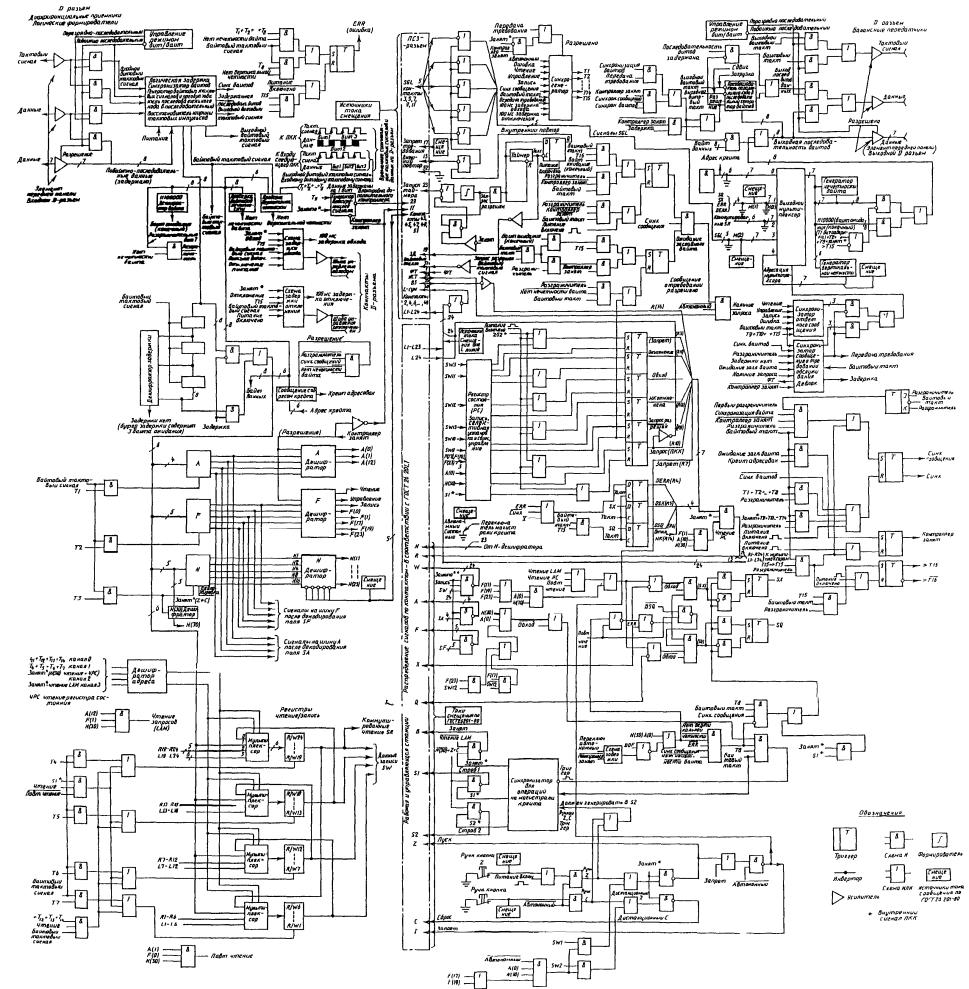

32 Информационные и тактовые сигналы

Примечание. Стандарты для информационного и тактового сигналов у D-портов основаны на стандарте RS-422 Ассоциации промышленников по радио, электронике и телевидению (Electronic Industries Association)*. Этот стандарт тесно связан с предварительной рекомендацией V11 C.C.I.T.T:

Международный консультативный комитет по телеграфу и телефону (Женева, Швейцария). Предварительная рекомендация Х27 «Электрические характеристики согласованных схем обмена двойных токов для общего использования с оборудованием интегральных схем в области передачи информации»**.