ГОСУДАРСТВЕННЫЙ СТАНДАРТ СОЮЗА ССР

ФАСТБАС

МОДУЛЬНАЯ БЫСТРОДЕЙСТВУЮЩАЯ

СИСТЕМА

СБОРА ДАННЫХ

ГОСТ 34.340-91

(МЭК 935-90)

КОМИТЕТ СТАНДАРТИЗАЦИИ И МЕТРОЛОГИИ СССР

Москва

СОДЕРЖАНИЕ

ПРЕДИСЛОВИЕ

1. Официальные решения или соглашения МЭК по техническим вопросам, подготовленные техническими комитетами, в которых представлены все заинтересованные национальные комитеты, выражают с возможной точностью международную согласованную точку зрения по рассматриваемым вопросам.

2. Решения представляют собой рекомендации для международного пользования и в этом виде принимаются национальными комитетами.

3. В целях содействия международной унификации МЭК выражает пожелание, чтобы все национальные комитеты приняли текст рекомендаций МЭК в качестве своих национальных стандартов, насколько это позволят условия каждой страны. Любые расхождения между рекомендациями МЭК и соответствующими национальными стандартами должны быть, по возможности, четко изложены в стандартах.

4. МЭК не дает каких-либо критериев обозначения соответствия оборудования рекомендациям МЭК и не несет ответственности в случае заявления, что оно соответствует требованиям хотя бы одной из них.

ПРЕДИСЛОВИЕ НАУЧНОГО РЕДАКТОРА РУССКОГО ТЕКСТА

Техническое задание на разработку системы Фастбас было сформулировано группой ядерных электронщиков, работающих в ведущих институтах США, к июлю 1977 г. Разработку стандарта финансировало Министерство энергетики. Разработчики собирались для обсуждения промежуточных результатов и возникающих проблем не реже чем раз в квартал в течение пяти лет. К 1980 г. появилась первая версия стандарта, затем ежеквартально выпускались обновленные версии. Специалисты европейских институтов, объединенные комитетом European Standards on Nuclear Electronics (ESONE), анализировали версии и предлагали свои рекомендации. К ноябрю 1982 г. разработка была завершена - комитет Nuclear Instruments Modules (NIM) объявил о принятии стандарта.

Началась разработка аппаратуры в стандарте Фастбас. Наиболее значительные результаты публиковал и публикует журнал «IЕEE Transactions on Nuclear Science».

На основе накопившегося опыта стандарт Фастбас был уточнен и в 1986 г. стал национальным стандартом США ANSI/IEEE Std 960-1986. В сентябре 1983 г. стандарт был представлен в Технический комитет № 45 Международной электротехнической комиссии, а в январе 1987 г. ТК 45 принял решение о публикации стандарта Фастбас в качестве стандарта МЭК-935, он вышел в свет в июне 1990 г. Настоящий стандарт является аутентичным переводом стандарта.

В Приложении А.1 в качестве примера описана реализация логического протокола Фастбас на быстродействующих ЭСЛ-элементах. Большая плата модуля размером (366,7×400) мм позволяет разместить большое число ЭСЛ-микросхем и рассеять мощность до 75 Вт на каждый модуль единичной ширины. Этот вариант реализации нацелен на создание наиболее быстродействующей стационарной аппаратуры.

В гл. 12 оговорена возможность реализации протокола на элементах любого типа. Учитывая это, группа специалистов (С.Г. Басиладзе, В.В. Кипаренко, О.А. Никольский, В.Н. Тресоруков и К.Э. Эрглис) предложила реализовать протокол Фастбас на экономичных ТТЛ- и КМОП-микросхемах при БТЛ-уровнях сигналов в магистрали. Более высокая степень интеграции микросхем и малое потребление энергии позволили уменьшить размеры модулей и крейтов, обеспечивая возможность применения аппаратуры в цехах и на бортах. Было предложено также дополнить стандарт выборкой байтов данных и модификацией длины адресного слова. Расширение стандарта Фастбас описано в приложении А.2, которое подготовил К. Эрглис при участии С. Басиладзе.

Весной 1987 г. проект настоящего стандарта (в виде перевода проекта стандарта МЭК с дополнением А.2) был разослан в 30 предприятий разных ведомств. Из 23 ответивших предприятий 12 высказались за использование расширенного стандарта Фастбас в качестве основы Единой системы магистрально-модульной многопроцессорной информационно-измерительно-управляющей аппаратуры (ЕС МММИИУА), а остальные предприятия предложили использовать другие стандарты.

Следует особо отметить две характеристики стандарта Фастбас: точное определение функций каждого бита в стандартизованных регистрах управления и состояний (гл. 8) и описание логического протокола соединителей сегментов (гл. 10).

Стандартизация функций битов РУС позволила создать второй стандарт Фастбас - Fastbus Standard Routines (IEEE Std 1177-1989 или МЭК-1052 (апрель 1991 г.), который определяет специализированный макроассемблер для программирования операций на магистралях Фастбас. Этот стандарт в переводе на русский язык также целесообразно издать в качестве Государственного стандарта.

Протокол соединителей сегментов содержит, в частности, правила определения маршрутных таблиц, запоминаемых в соединителях. Это позволило создавать информационные сети произвольной конфигурации при высокой их надежности и живучести. В настоящее время в IEEE завершается разработка третьего стандарта Фастбас на наиболее прогрессивную оптоволоконную сеть при последовательной передаче информации.

Об организации разработки стандартов Фастбас можно судить по списку участников, которым открываются национальные стандарты. Перевод на русский язык выполнили К.Э. Эрглис, А.Д. Росляков и А.В. Шалаев.

В совокупности стандарты Фастбас определяют 5 уровней модели открытых систем, при этом программирование является единым как для передач между модулями внутри крейта, так и для передач между крейтами в локальной сети Фастбас произвольной формы. Комплекс из трех стандартов Фастбас обеспечит возможность создания наиболее эффективных систем МММИИУА разной мощности и назначения при минимальных стоимостях разработки, программирования, производства и эксплуатации.

ВВЕДЕНИЕ

Настоящий стандарт подготовлен Техническим комитетом 45 «Ядерное приборостроение» МЭК. Текст стандарта основан на следующих документах:

|

По правилу шести месяцев |

Отчет о голосовании |

|

45 (ЦБ) 182 |

45 (ЦБ) 186, 186А |

Полную информацию о голосовании за утверждение данного стандарта можно получить из Отчетов о голосовании, указанных в таблице.

В стандарте имеются ссылки на следующие Публикации МЭК:

113-7-(1981) (ГОСТ 2.743-82) Диаграммы, чертежи, таблицы. Часть 7. Подготовка логических диаграмм.

169-10 (1983)* Радиочастотные соединители. Часть 10. Радиочастотные коаксиальные соединители с внутренним диаметром внешнего проводника 3 мм (0,12 дюйма) с зажимным сочленением. Волновое сопротивление 50 Ом (тип SMB).

* Данная Публикация МЭК находится в фонде стандартов ТК 22 (НПО «Персей»)

297-1 (1982) (ГОСТ 28601.1-90) Конструкции несущие серии 482,6 мм (19 дюймов). Часть 1. Панели и стойки.

516 (1975) (ГОСТ 27080-86) Модульная система приборов для обработки данных. Система КАМАК.

547 (1976)* Вставной модуль и стандартный 19-дюймовый каркас для размещения модулей по стандарту NIM (для ядерного приборостроения).

* Данная Публикация МЭК находится в фонде стандартов ТК 22 (НПО «Персей»)

ГОСУДАРСТВЕННЫЙ СТАНДАРТ СОЮЗА ССР

|

ФАСТБАС Модульная быстродействующая система сбора данных Fastbus. Modular high speed data acquisition system |

ГОСТ (МЭК 935) |

Дата введения 01.07.92

ГЛАВА 1. НАЗНАЧЕНИЕ, ОБЛАСТЬ ПРИМЕНЕНИЯ И ВВОДНЫЙ ОБЗОР

Данный раздел включает назначение и область применения данного стандарта, а также вводный обзор.

1.1. Назначение и область применения

Настоящий стандарт определяет магистрально-модульную систему для сбора данных, их обработки и управления.

Приведены механические, сигнальные, электрические и протокольные спецификации, достаточные для обеспечения совместимости между блоками, выполненными разными разработчиками и производителями.

Данный стандарт применим к системам, состоящим из модульных блоков электронных приборов, которые обрабатывают или передают данные или сигналы и обычно связаны с компьютерами или другими автоматическими устройствами обработки данных.

Стандарт применим для ядерного приборостроения и систем управления, но может применяться также и в других областях.

Положения стандарта являются рекомендуемыми. При применении стандарта обязательными являются требования, заключённые в рамку.

1.2. Введение и общие сведения

Система ФАСТБАС состоит из множества магистральных сегментов, которые могут работать независимо, но связаны друг с другом для передачи данных и другой информации. ФАСТБАС может работать асинхронно с использованием протокола подтверждений, чтобы эффективно сочетать устройства различного быстродействия без предварительного учета скорости их работы. Система способна работать и синхронно без подтверждений при передаче блоков данных с максимальной скоростью.

Сложные системы, такие как ФАСТБАС, легче понимать, если спецификации сопровождаются общими описаниями, которые раскрывают значение деталей в целой системе. Эта глава содержит обзор главных характеристик и операций ФАСТБАС. В большинстве следующих глав имеются, в дополнение к обязательным составляющим спецификации, примеры использования стандартизуемых возможностей системы. В гл. 2 представлены определения терминов, которые имеют специальный смысл в системах ФАСТБАС. Определены символы, применяемые в схемах для обозначения различных частей системы ФАСТБАС, а также дан список обычно используемых сокращений. В остальных главах изложены спецификации системы. Эти главы сопровождаются рядом приложений, которые дают более детальную информацию о некоторых особенностях ФАСТБАС. В этой главе слова, имеющие специальный смысл в системе ФАСТБАС, выделены прописными буквами.

Большинство характеристик ФАСТБАС определились из рассмотрения требований, предъявляемых к современным, системам сбора и обработки данных. Требование быстродействия удовлетворяется параллельной работой многих процессоров, которые могут сообщаться друг с другом, а также с устройствами для сбора данных и управления. Протокол связи, используемый процессорами и устройствами, предусматривает большие поля адресов и данных. Протокол определен независимо от технологического воплощения интегральных схем, чтобы иметь возможность реализовать преимущества прогрессивных технологий, гибкость систем обеспечивается модульностью, которая допускает множество вариантов конфигурации систем.

Модульные системы отличаются методами связи устройств, образующих систему. Должны быть стандартизованы механические, электрические и логические соединения. Электрические соединения осуществляются набором сигнальных линий, которому дано название СЕГМЕНТ. ФАСТБАС-УСТРОЙСТВА могут быть соединены просто при помощи КАБЕЛЬ-СЕГМЕНТОВ, однако такая компоновка может повлечь за собой снижение скорости. В локальных устройствах необходимые свойства достигаются объединением нескольких МОДУЛЕЙ в КРЕЙТЕ, чтобы использовать общую магистраль, располагаемую на задней панели (рис. 1). Эта магистраль, называемая КРЕЙТ-СЕГМЕНТОМ или СЕГМЕНТОМ, как и КАБЕЛЬ-СЕГМЕНТ, образует логический блок системы ФАСТБАС.

Используя ФАСТБАС-протокол, СЕГМЕНТ работает как автономная магистраль, связывающая один или более УСТРОЙСТВ-МАСТЕРОВ с рядом УСТРОЙСТВ-СЛУГ. При выполнении всех операций на магистрали устанавливается соотношение между МАСТЕРОМ и СЛУГОЙ, при котором инициатором должен быть МАСТЕР, а отвечающим - СЛУГА. МАСТЕР способен запрашивать и получать управление сегментом, к которому он присоединен, чтобы связываться со СЛУГОЙ. Если связь устанавливается с другим МАСТЕРОМ, то на время операции отвечающий МАСТЕР действует как СЛУГА. СЛУГА не может получить право владения магистралью, но может сделать запрос на обслуживание тому МАСТЕРУ на том же СЕГМЕНТЕ, который способен начать процедуру обслуживания запроса. МАСТЕРА располагают более разнообразным механизмом прерываний, благодаря которому они могут овладеть магистралью и записать сообщение о прерывании в устройство обслуживания прерываний.

1 - крейт; 2 - соединение сегмента с другими сегментами, интерфейсом процессора и т.п.; 3 - к модулю соединителю сегментов; 4 - вставные модули: мастер, слуга, соединитель сегментов, специального назначения; 5 - крейт-сегмент (магистраль на задней плате); 6 - разъемы крейт-сегмента; 7 - вспомогательные разъемы крейта

Рис. 1. Основные элементы системы ФАСТБАС

При нескольких МАСТЕРАХ в СЕГМЕНТЕ должны быть предусмотрены средства для урегулирования одновременных запросов на пользование магистралью. Каждому МАСТЕРУ присвоен Уровень арбитража, который он использует во время Циклов арбитража. В ответ на таймирующие сигналы, получаемые от управления таймированием арбитража, которое принадлежит СЕГМЕНТУ, схема в каждом МАСТЕРЕ определяет, какому из претендующих МАСТЕРОВ будет отдано владение магистралью. Процедура арбитража обычно не вызывает потерь времени, поскольку следующий МАСТЕР может быть определен до того, как действующий МАСТЕР закончит свою операцию.

Несколько МАСТЕРОВ, расположенных в одном СЕГМЕНТЕ, используют общую магистраль. С точки зрения МАСТЕРА соревнование за право владения магистралью может снизить ее пропускную способность из-за потерь времени на ожидание. Поскольку СЕГМЕНТЫ работают независимо, распределение МАСТЕРОВ по нескольким СЕГМЕНТАМ может смягчить проблему соревнования и увеличить пропускную способность благодаря тому, что информация, нужная каждому МАСТЕРУ, может быть локализована в его СЕГМЕНТЕ.

1 - процессор-хозяин; 2 - интерфейс процессора; 3 - согласователь; 4 - кабель-сегмент; 5 - соединитель сегментов; 6 - мастер; 7 - крейт-сегмент (согласованный); 8 - слуги

Рис. 2. Пример топологии системы ФАСТБАС

МАСТЕР в данном СЕГМЕНТЕ должен также быть способным быстро связываться со СЛУГОЙ, расположенным в другом СЕГМЕНТЕ. Эта способность обеспечивается СОЕДИНИТЕЛЯМИ СЕГМЕНТОВ (СС), которые временно связывают независимые СЕГМЕНТЫ (рис. 2).

Все СЕГМЕНТЫ, выполняющие операцию, должны быть в то же время доступны для проведения межсегментной операции. Механизм арбитража, наряду с соответствующими схемами в каждом соединителе СЕГМЕНТОВ СС, обеспечивает разрешение проблем соревнования за магистраль для МАСТЕРОВ, находящихся как в данном, так и в других СЕГМЕНТАХ. Поскольку данный СЕГМЕНТ может быть связан с любым из ряда различных СЕГМЕНТОВ, могут быть реализованы такие конфигурации систем, в которых пути передачи информации оптимизированы с уменьшением затрат времени.

Среда, через которую сообщаются два СС, расположенные в разных СЕГМЕНТАХ, не стандартизована, это позволяет выбирать канал связи, наиболее подходящий для данного применения. Для таких соединений возможно использовать КАБЕЛЬ-СЕГМЕНТОВ совместно с эффективными средствами, стандартизованными в приложении Е. С КАБЕЛЬ-СЕГМЕНТОМ, кроме СС, могут быть соединены и другие устройства. Такие устройства также следуют ФАСТБАС-протоколу, имеют переключателе для кодирования входного адреса при ГЕОГРАФИЧЕСКОЙ АДРЕСАЦИИ и должны быть снабжены питанием.

Другие технические приемы связи СЕГМЕНТОВ включают использование БУФЕРИРОВАННЫХ МЕЖСОЕДИНЕНИЙ и РАСШИРИТЕЛЕЙ СЕГМЕНТОВ. БУФЕРИРОВАННОЕ МЕЖСОЕДИНЕНИЕ представляет собой устройство, которое хранит в памяти и продвигает операции ФАСТБАС, разрушая таким образом синхронизм между мастером и слугой. Концепция РАСШИРЕННОГО СЕГМЕНТА позволяет нескольким СЕГМЕНТАМ пользоваться одним АДРЕСОМ ГРУППЫ. Такое коллективное пользование достигается применением РАСШИРИТЕЛЕЙ СЕГМЕНТА, простота которых в сравнении с СОЕДИНИТЕЛЯМИ СЕГМЕНТОВ достигается за счет некоторого снижения гибкости в топологии системы и операциях для членов РАСШИРЕННОГО СЕГМЕНТА.

В большинстве случаев, если не всегда, МАСТЕРА должны иметь некоторые способности процессоров. При проектировании систем ФАСТБАС возникает также нужда в присоединении к системе больших и малых ЭВМ. Такое соединение выполняется при помощи ИНТЕРФЕЙСА-ПРОЦЕССОРА, который создает внешнему процессору доступ к ФАСТБАС-системе через КАБЕЛЬ или КРЕЙТ-СЕГМЕНТ (рис. 2). Системные требования диктуют необходимость иметь в каждой системе один процессор с полной информацией о структуре системы. В частности, он должен иметь доступ к любому СЕГМЕНТУ системы и знать, как СЕГМЕНТЫ соединены друг с другом. Этот процессор, названный ПРОЦЕССОРОМ-ХОЗЯИНОМ, инициирует систему, сообщая каждой стороне каждого СС, какие операции он должен передать в следующий СЕГМЕНТ. Используя ГЕОГРАФИЧЕСКУЮ АДРЕСАЦИЮ, ПРОЦЕССОР-ХОЗЯИН может выяснить местоположение и тип каждого УСТРОЙСТВА в системе и, если нужно, присвоить ЛОГИЧЕСКИЕ АДРЕСА УСТРОЙСТВАМ. ЛОГИЧЕСКИЕ АДРЕСА позволяют УСТРОЙСТВУ использовать поле ВНУТРЕННИХ АДРЕСОВ, приспособленное для нужд и независимое от положения УСТРОЙСТВА внутри СЕГМЕНТА.

Главные характеристики и возможности системы ФАСТБАС можно суммировать следующим образом:

· Скорость ограничена только задержками распространения сигнала в среде и задержками алогических схемах, скорость обычно лучше чем 10 МГц при элементах ЭСЛ.

· Большие поля адресов и данных (32 бита);

· Сегментированная магистраль, допускающая параллельную работу сегментов;

· Способность к соединениям во всем объеме системы;

· Передача блоков данных с подтверждением или принудительная передача;

· Единый протокол во всем объеме системы;

· Наличие механизмов прерываний и арбитража.

1.2.1. ФАСТБАС-операции

ФАСТБАС-операции, описанные в гл. 5, выполняются при помощи многолинейной магистрали, назначение линий и сигналов в которой показано в табл. I. КАБЕЛЬ-СЕГМЕНТ состоит из 60 линий, указанных в верхней части списка. КРЕЙТ-СЕГМЕНТ содержит дополнительно другие линии, а также линии питания. Сигналы классифицированы в таблице в соответствии с применением:

Т - таймирование в циклах адреса и передачи данных;

У - управление в циклах адреса и передачи данных;

И - информация в циклах адреса и передачи данных;

А - асинхронный - таймирование не связано непосредственно с передачами информации;

ТА - таймирование арбитража;

ИА - информация о состоянии линий арбитража;

УА - управление арбитражем;

П - последовательные данные, их таймирование не зависит от работы параллельной магистрали;

Ф - фиксированная информация;

С - специальное назначение.

Большинство ФАСТБАС-операций начинается с запроса МАСТЕРА и предоставления ему владения магистралью. Затем МАСТЕР выбирает СЛУГУ первичным адресным циклом, сопровождая его любым числом циклов передачи данных, после этого магистраль освобождается.

Первичный адресный цикл начинает МАСТЕР, выставляя адрес СЛУГИ на 32 линии AD-адрес / данные и выдавая затем сигнал AS-строб адреса. Выставление адресного слова определяет путь (если нужно - через СОЕДИНИТЕЛИ-СЕГМЕНТОВ) между МАСТЕРОМ и СЛУГОЙ. Когда СЛУГА узнает свой адрес, он отвечает сигналом АК-подтверждение приема адреса. Протокол требует, чтобы сигналы AS и АК оставались на линиях до полного завершения операции.

Связка AS/AK побуждает все другие устройства не замечать работу магистрали, позволяя связавшейся паре выполнять любой понятный им протокол, пока не разорвана связь AS/AK. Для наиболее употребительных операций определены стандартные протоколы, чтобы облегчить разработку совместных УСТРОЙСТВ.

Сигналы ФАСТБАС

|

Обозначение |

Название сигнала |

Применение |

Число |

Примечание |

||

|

AS |

Строб адреса |

Т |

1 |

|

|

Для адресации и извещения о статусе соединения |

|

АК |

Подтверждение приема адреса |

Т |

1 |

|

||

|

EG |

Разрешение географической адресации |

У |

1 |

|

||

|

MS |

Выбор режима передачи |

У |

3 |

|

||

|

RD |

Чтение |

У |

1 |

|||

|

AD |

Адрес/данные |

И |

32 |

Для данных и управления передачей данных |

||

|

PA |

Четкость |

И |

1 |

|||

|

РЕ |

Разрешение контроля по четкости |

И |

1 |

|||

|

SS |

Статус СЛУГИ |

И |

3 |

|||

|

DS |

Строб данных |

т |

1 |

|||

|

DK |

Подтверждение приема данных |

т |

1 |

|||

|

WT |

Ожидание |

А |

1 |

|

|

|

|

SR |

Запрос на обслуживание |

А |

1 |

|

|

|

|

RB |

Сброс магистрали |

А |

1 |

|

|

|

|

BH |

Магистраль остановлена |

У |

1 |

|

|

|

|

AG |

Разрешение на арбитраж |

ТА |

1 |

|

|

Для арбитража магистрали |

|

AL |

Уровень арбитража |

ИА |

6 |

|

||

|

AR |

Запрос на арбитраж |

А |

1 |

|

||

|

AI |

Запрет запроса на арбитраж |

УА |

1 |

|

||

|

GK |

Подтверждение приема разрешения на арбитраж |

ТА |

1 |

|

||

|

|

60 |

|

|

|

||

|

ТХ |

Передающая последовательная линия |

П |

1 |

|

|

|

|

RX |

Приемная последовательная линия |

п |

1 |

Для протокола последовательной сети ФАСТБАС |

||

|

GA |

Штырьки географического адреса* (кодирование позиции, не соединены линиями) |

ф |

|

|

|

|

|

ТР |

ТР-штырек* (не соединен с линией) |

с |

1 |

|

|

|

|

DL |

Цепная связь налево |

с |

3 |

|

|

|

|

DR |

Цепная связь направо |

с |

3 |

|

Только на крейт-сегменте |

|

|

TR |

Согласованная линия ограниченного применения |

с |

8 |

|

|

|

|

UR |

Несогласованная линия ограниченного применения |

с |

2 |

|

|

|

|

FP |

FP-штырьки (без линии, свободное использование) |

|

4 |

|

|

|

|

R |

Зарезервированы |

|

5 |

|

|

|

* Вместо штырьков GA и ТР на КАБЕЛЬ-СЕГМЕНТЕ применяются переключатели-регистры.

По получении подтверждения АК от СЛУГИ МАСТЕР снимает код адреса с линий AD и использует эти линии для передачи данных в последующих циклах. После того, как связка AS/AK между МАСТЕРОМ и СЛУГОЙ установлена, МАСТЕР может начать операцию чтения выдачей сигналов на линию чтения (RD) и линию строб данных (DS), как показано на рис. 3. СЛУГА отвечает выставлением данных на линиях AD и выдачей сигнала DK - подтверждение приема данных. Этот сигнал использует МАСТЕР, чтобы взять данные.

При операции записи МАСТЕР выставляет данные на линиях AD и сопровождает это выставление сигналом DS - строб данных. СЛУГА отвечает выдачей DK - подтверждение приема данных. Операция отличается тем, что МАСТЕР снимает с магистрали все свои сигналы, включая AS. СЛУГА, обнаружив удаление AS, снимает свои сигналы, включая АК.

Поскольку циклы адреса и передачи данных легко различимы, МАСТЕР использует три линии выбора режима (MS <2:0>) как для модификации значения адресной информации, так и для того, чтобы независимо задать тип передачи данных. В первичном адресном цикле могут быть указаны одиночные данные, вторичный адрес, а также передача блока данных с подтверждением или принудительная передача - без подтверждения.

Подобным образом, три линии информации о статусе СЛУГИ (SS <2:0>) используют для индикации успешных циклов адреса и передачи данных или для сообщения о причинах неудачи. Трудности адресации могут возникать в СОЕДИНИТЕЛЯХ-СЕГМЕНТОВ из-за того, что они иногда не отвечают МАСТЕРУ, вследствие неисправности схемы или не могут получить доступ к СЕГМЕНТУ, присоединенному к дальней стороне и занятому, или СС заблокированы операцией с более высоким приоритетом. Зависание в магистрали, вызванное адресацией к несуществующему устройству в СЕГМЕНТЕ назначения, устраняется таймерами в МАСТЕРЕ или в том соединителе СС, который выдал адрес в СЕГМЕНТ назначения.

1 - адрес; 2 - данные

Рис. 3. Основная операция чтения с подтверждением (с точки зрения мастера)

В течение цикла передачи данных СЛУГА, в дополнение к способности показать, что он не может больше принимать данные или не имеет больше данных для передачи, может также сообщать, что в настоящий момент он занят или обнаружил ошибку одного из нескольких классов.

При передаче данных ФАСТБАС может быть применен контроль четности и должны быть обеспечены рекомендованные технические приемы для устранения ошибок. При операциях записи СЛУГИ обычно реагируют на ошибки передачи игнорированием правильных данных и сигнализируют МАСТЕРУ о том, что произошла ошибка. МАСТЕР может затем повторить операцию. Устранение ошибок при операциях считывания является более сложным. СЛУГА обычно бывает не осведомлен об ошибке и может прирастить свой внутренний указатель адреса или иметь доступ к регистру типа «Первый вошел - первый вышел» или к регистру с очисткой после чтения, следовательно, данные могут быть не доступны для повторной передачи. Для поддержки устранения ошибок при считывании может быть введен в работу ЗАЩИТНЫЙ БУФЕР.

ЗАЩИТНЫЙ БУФЕР всегда содержит копию последних данных, переданных СЛУГЕ или от СЛУГИ. Следовательно, путем введения подходящего ЗАЩИТНОГО БУФЕРА МАСТЕР может повторно обратиться к данным после ошибки в считывании.

1.2.2. Соединители сегментов СС

СОЕДИНИТЕЛЬ СЕГМЕНТОВ управляет деятельностью двух СЕГМЕНТОВ, которые он соединяет, ожидая появление адреса, который числится в списке адресов, запрограммированных для узнавания. На узнанный адрес, поступивший от одного из СЕГМЕНТОВ на ближнюю сторону, СС реагирует запросом на использование другого СЕГМЕНТА, присоединенного к дальней стороне, и выставлением данного адреса на этот СЕГМЕНТ после овладения его магистралью. Два СЕГМЕНТА остаются связанными друг с другом до тех пор, пока we закончится операция. Адрес, выставленный на дальней стороне, может, в свою очередь, быть узнан другим СОЕДИНИТЕЛЕМ СЕГМЕНТОВ и передан следующему СЕГМЕНТУ. В зависимости от потребителей данной операции может быть связано произвольное число СЕГМЕНТОВ. Адрес содержит всю информацию, необходимую для того, чтобы соответствующие СС образовали правильные соединения.

Для того, чтобы в адресе удобно располагалась информация о маршруте сообщения, полное адресное поле, доступное в системе, разделено между СЕГМЕНТАМИ таким образом, что старшие разряды кода адреса определяют адрес СЕГМЕНТА. Эта старшая часть адреса называется полем АДРЕСА ГРУППЫ (GP). СЕГМЕНТУ могут быть присвоены одно или несколько значений GP, если расположенные в нем устройства требуют большого объема адресации. УСТРОЙСТВА в СЕГМЕНТЕ различаются АДРЕСОМ МОДУЛЯ, который примыкает к полю GP и может включать несколько младших разрядов из поля GP. Комбинация из полей АДРЕСА ГРУППЫ и АДРЕСА МОДУЛЯ образует АДРЕС УСТРОЙСТВА, который служит для определения УСТРОЙСТВА в любом месте системы. Остающиеся младшие разряды адреса или ПОЛЕ ВНУТРЕННЕГО АДРЕСА служат для определения части УСТРОЙСТВА или его функций. Благодаря возможности проведения специального цикла передачи данных, называемого вторичным адресным циклом, число различных адресуемых частей или функций внутри устройства не ограничено числом, которое может быть выражено полем внутреннего адреса.

В простых СОЕДИНИТЕЛЯХ СЕГМЕНТОВ старшие разряды адреса используют для адресации к внутренней памяти, которая содержит таблицу адресов, подлежащих передаче. Во время инициации системы в память каждого СС вводится маршрутная таблица, необходимая для направления всех разрешенных операций.

Эта схема не создает ограничений на конфигурации связей между СЕГМЕНТАМИ. Например, они могут быть соединены в древовидную структуру с большой ЭВМ при стволе и устройствами для сбора данных на концах ветвей. Если между двумя СЕГМЕНТАМИ, расположенными в разных концах системы, требуется обеспечить большой поток информации, который мог бы загрузить промежуточные СЕГМЕНТЫ, целесообразно использовать КАБЕЛЬ-СЕГМЕНТ, чтобы обойти промежуточные СЕГМЕНТЫ. При таком добавлении не требуется изменять адреса УСТРОЙСТВ, достаточно задать в СС новые маршрутные таблицы, чтобы освободить промежуточные СЕГМЕНТЫ от излишних передач. По этой схеме могут быть реализованы древовидные, звездообразные, кольцевые и другие структуры.

Когда МАСТЕР начинает ФАСТБАС-операцию, он всегда запускает внутренний таймер ответных действий на время, достаточное для работы в данном СЕГМЕНТЕ. Если операцию нужно провести через один или более соединителей сегментов, МАСТЕР должен быть осведомлен о дополнительных задержках, которые встретятся, прежде чем будет получен ответ. Каждый СС, передающий операцию, выставляет сигнал ожидание WT в СЕГМЕНТ, из которого пришла операция, и запускает таймер на время, подходящее для СЕГМЕНТА, которому операция передается. Сигнал WT заставляет любого МАСТЕРА (а СС действует как МАСТЕР в том СЕГМЕНТЕ, в который он передает операцию) остановить свои таймер. Этот таймер запускается снова при снятии сигнала WT. Таким образом, операция проходит весь свой путь через систему без превышения лимитов времени, за исключением, разумеется, тех случаев, когда попадается СЕГМЕНТ, который не дает нормального подтверждения или не выставляет сигнал WT. В каждом МАСТЕРЕ имеется удлиняемый таймер, обнаруживающий тупиковые ситуации, которые могут возникать, например, при конфликтных запросах. После превышения лимита времени МАСТЕР ждет в течение случайного времени выдержки, прежде чем снова пытаться выполнить операцию.

1.2.3. Регистры управления и статуса

Область адресов некоторых регистров и функций в УСТРОЙСТВАХ желательно отделить от области нормальных регистров данных, чтобы предусмотреть защиту от случайного доступа и при этом не прерывать размещение областей адресов нормальных данных. Например, требуется чтобы два УСТРОЙСТВА памяти имели адресные области, расположенные рядом в адресном пространстве, чтобы их можно было использовать как одну большую память. Однако эти УСТРОЙСТВА могут содержать управляющие и статусные регистры, предназначенные для защиты памяти или обнаружения, или исправления ошибок, причем эти регистры также должны быть доступны. Более того, желательно, чтобы УСТРОЙСТВА имели основные статусные и информационные регистры в стандартном размещении, чтобы они были прямо доступны для программы со стандартными подпрограммами.

Для выполнения этих требований был использован метод выбора области адресов регистров управления и статуса (CSR) в первичном адресном цикле соответствующим кодированием линий MS. Во вторичном адресном цикле в области адресов CSR выбирается регистр, а затем в цикле передачи данных происходит передача к регистру или от него. Вторичная адресация предусматривает использование внутри УСТРОЙСТВА полного 32-разрядного адреса; такое адресное пространство достаточно для удобных стандартных размещений без опасения нехватки адресов. В предназначенных CSR-регистрах определены стандартные места для всех обычных управляющих и статусных битов. Рекомендуется встраивать в УСТРОЙСТВО регистр-идентификатор, уникальный для УСТРОЙСТВА данного типа и применяемый при инициализации систем. Биты идентификатора входят в статусный регистр 0, благодаря этому даже простые УСТРОЙСТВА без адресных дешифратов могут правильно реагировать на вызов, причем это достигается малым увеличением стоимости.

1.2.4. Географическая адресация

Наиболее общей формой адресацией к УСТРОЙСТВУ является логическая адресация, при которой адрес УСТРОЙСТВА не зависит от его физического положения в системе. Однако система ФАСТБАС имеет и ГЕОГРАФИЧЕСКУЮ АДРЕСАЦИЮ, при которой УСТРОЙСТВО выбирается по номеру в его физической позиции в СЕГМЕНТЕ, благодаря этому всегда возможно найти УСТРОЙСТВО с целью записи или проверки. ГЕОГРАФИЧЕСКАЯ АДРЕСАЦИЯ должна применяться для инициализации систем, в которых адресные регистры устанавливаются программно. Когда на такую систему подают питание, регистры, которые будут содержать информацию об АДРЕСЕ УСТРОЙСТВА, устанавливаются случайным образом. ГЕОГРАФИЧЕСКАЯ АДРЕСАЦИЯ используется для выбора УСТРОЙСТВА с целью загрузить их адресные регистры надлежащим содержимым. Первые 256 адресов в каждом СЕГМЕНТЕ зарезервированы для специальных целей, а первые 32 из них используются для ГЕОГРАФИЧЕСКОЙ АДРЕСАЦИИ. В КРЕЙТ-СЕГМЕНТЕ на каждой позиции модуля имеется сегментный раздел, в котором 5 штырьков кодированы (GA4 - GA0). Кодированное число 0 обозначает крайнюю правую позицию, если смотреть на крейт со стороны передней панели. Кодированное число возрастает на единицу при перемещении на одну позицию влево. Когда на магистрали выставлен ГЕОГРАФИЧЕСКИЙ АДРЕС (от 0 до 31), управляющая линия EG - разрешение географической адресации - возбуждена или вспомогательной логикой сегмента, или действующим МАСТЕРОМ. Когда во время первичного адресного цикла выдан сигнал EG, УСТРОЙСТВА сопоставляют код на своих штырьках с кодом пяти младших адресных битов на AD-линиях и отвечают, если обнаруживают совпадение кодов. Все УСТРОЙСТВА должны иметь эту способность, в то время как ЛОГИЧЕСКАЯ АДРЕСАЦИЯ не является обязательной.

Механизм ГЕОГРАФИЧЕСКОЙ АДРЕСАЦИИ может быть использован для доступа к управляющим информационным регистрам в неинициированных УСТРОЙСТВАХ, благодаря этому процедуры инициации могут выполняться автоматически. Обычные схемы узнавания логического адреса в устройстве не задействованы до тех пор, пока не выполнена инициализация.

1 - адрес; 2 - данные

Рис. 4. Передача блока с записями (с точки зрения мастера)

УСТРОЙСТВА, присоединяемые к КАБЕЛЬ-СЕГМЕНТУ, должны иметь переключаемые регистры для ручного задания и хранения ГЕОГРАФИЧЕСКОГО АДРЕСА.

1.2.5. Передача блока и принудительная передача блока

Операция передачи блока состоит из адресного цикла и любого числа циклов передачи данных одного типа - или все циклы чтения, или запись. Соединение между МАСТЕРОМ и СЛУГОЙ выполняется, как описано выше - с полным подтверждением как в начале, так и в конце операции. Скорость увеличена использованием обоих фронтов в паре сигналов строб данных и подтверждением приема данных DS/DK, при этом все же предусмотрена полная защита передачи данных благодаря подтверждениям. На рис. 4 показана передача блока с записями.

Возможна передача блока без подтверждений в циклах передачи данных. Такая принудительная передача блока допустима между УСТРОЙСТВАМИ, которые могут работать с одинаковой скоростью передачи данных. Например, в случае записи после первоначального подтверждения в адресном цикле с установлением связки AS/AK, МАСТЕР просто выставляет слова данных и выдает фронты DS с подходящей скоростью. Ответы DK как средство таймирования игнорируются, но их следует использовать для подсчета числа переданных слов с целью контроля. При такой работе сигнал DS становится строб-сигналом, который использует СЛУГА, чтобы находить слова данных в синхронной передаче. В случае чтения МАСТЕР выдает DS в качестве тактовых импульсов, которые СЛУГА использует для определения скорости передачи и сопровождает данные сигналом DK, который МАСТЕР воспринимает как строб данных.

В операциях, защищенных подтверждениями, требуется, чтобы каждое слово данных находилось на магистрали по крайней мере в течение удвоенного времени распространения, пока данные проходят к пункту назначения и сигнал подтверждения идет обратно к источнику. Когда же подтверждения не используются, в одно и то же время на пути в многокрейтной системе могут проходить несколько слов данных, благодаря чему данные могут передаваться с максимальной скоростью, допускаемой магистралями.

В большинстве случаев в операциях желательно использовать полные подтверждения. В цикле передачи данных подтверждение позволяет обоим партнерам сделать, если нужно, паузу и досрочно закончить операцию (например, в случае переполнения буфера) при точном знании количества успешно переданных слов. В операциях без подтверждений в цикле передачи данных от МАСТЕРА требуется знание способности СЛУГИ и полосы пропускания всего пути, чтобы выбрать приемлемую тактовую частоту сигнала DS. Если есть запасы времени, лучше использовать более надежный режим работы с подтверждениями.

Если во время передачи блока МАСТЕР обнаруживает (через линию AR запроса на арбитраж), что другие УСТРОЙСТВА запрашивают магистраль, он может освободить магистраль и позднее возобновить передачу блока.

1.2.6. Операции с фиксированным адресом и заблокированным арбитражем

Описанные выше операции могут быть обобщены, если допустить поток данных в обратном направлении. Операции с фиксированным адресом содержит первичный адресный цикл, сопровождаемый любым числом вторичных адресных циклов и/или циклов передачи данных. Например, в течение цикла чтение-модификация-запись МАСТЕР выставляет адрес, читает данные, изменяет направление передачи на AD-линиях, снимая сигнал RD, и записывает модифицированные данные обратно в память СЛУГИ (см. рис. 5). Такая операция не может быть прервана каким-либо другим процессором, поскольку она все время скреплена связкой AS/AK и другое устройство не может попользовать магистраль. Образуется род неразделимой операции, необходимой в многопроцессорных системах для координации использования общих ресурсов.

1 - адрес; 2 - чтение; 3 - запись

Рис. 5. Операция с фиксированным адресом: чтение-модификация-запись. (с точки зрения мастера)

Непрерываемые операции могут быть расширены и далее, если МАСТЕР и СЛУГА согласятся о значении каждого цикла в магистрали, например, если адресный цикл, где связались МАСТЕР и СЛУГА, может сопровождаться вторичным адресным циклом, за которым следует еще один цикл передачи данных.

Операции с фиксированным адресом могут содержать передачи блоков. Направление потока данных может быть изменено между пересылками блоков или индивидуальными передачами слоев вне блоков.

Еще более общий вид операций в магистрали называется операцией с заблокированным арбитражем, при которой один МАСТЕР выполняет последовательность операций, направленных к нескольким различным ПЕРВИЧНЫМ АДРЕСАМ, при этом работа МАСТЕРА не может быть прервана никаким другим МАСТЕРОМ, поскольку действующий МАСТЕР не позволяет проводить арбитраж. Это может быть очень полезно для таймирования работы группы СЛУГ, используемых несколькими процессорами: последовательность операции может быть проведена без помех со стороны других процессоров. Этот механизм действует даже в случае, когда СЛУГИ находятся в разных СЕГМЕНТАХ, поскольку СОЕДИНИТЕЛЬ СЕГМЕНТОВ сделан так, что сохраняет любое соединение до тех пор, пока МАСТЕР не освободит магистраль для арбитража.

1.2.7. Сканирование редких данных

Во многих экспериментах не все УСТРОЙСТВА получают данные при каждом событии. Механизм сканирования редких данных позволяет быстро определить УСТРОЙСТВА, содержащие ценные данные. Для этого используются ТР-штырьки, не соединенные линиями магистрали и расположенные по одному на каждой позиции задней панели. ТР-штырек в позиции п присоединен к линии п адрес/данные. МАСТЕР, желающий начать сканирование редких данных, подает команду ШИРОКОЙ ОПЕРАЦИИ всем УСТРОЙСТВАМ СЕГМЕНТА, приглашая тех, кто имеет данные, выдать сигнал на свой ТР-штырек. Последующее чтение сигналов на AD-линиях показывает, какие именно УСТРОЙСТВА следует опросить для получения данных. Такая возможность может быть реализована и на КАБЕЛЕ-СЕГМЕНТЕ: достаточно подключить сигнал о наличии данных в УСТРОЙСТВЕ к выводу на соответствующую линию AD.

1.2.8. Широкие операции

При ШИРОКОЙ ОПЕРАЦИИ МАСТЕР может соединиться с более чем одним СЛУГОЙ во время одного первичного адресного цикла. ШИРОКАЯ ОПЕРАЦИЯ может быть использована в различных целях, например, для синхронизации УСТРОЙСТВ или для установки на нуль ряда счетчиков. Поскольку могут быть задействованы несколько СЛУГ, не возможны имеющие смысл подтверждения между МАСТЕРОМ и СЛУГОЙ. Однако системное подтверждение, получаемое от вспомогательной логики на каждом СЕГМЕНТЕ на любом пути, информирует МАСТЕРА, что его команда прошла к каждому из тех СЕГМЕНТОВ, к которым была адресована. МАСТЕР выставляет наряду с адресом также и код на линиях MS, чтобы показать, что выставлен ШИРОКИЙ АДРЕС. Специфический код в поле адресов указывает, является ли ШИРОКАЯ ОПЕРАЦИЯ ЛОКАЛЬНОЙ (только лишь в одном СЕГМЕНТЕ) или ГЛОБАЛЬНОЙ либо ко всем СЕГМЕНТАМ в сети, охватываемой информацией, хранимой в СОЕДИНИТЕЛЯХ СЕГМЕНТОВ, либо ко всем СЕГМЕНТАМ, расположенным в сети за определенным СЕГМЕНТОМ. В дополнение к возможности выбора СЕГМЕНТОВ при ШИРОКОЙ ОПЕРАЦИИ, поле адресов может быть использовано для выбора УСТРОЙСТВ заданного класса в достигаемых СЕГМЕНТАХ или для выбора функций, подлежащих выполнению.

В число определенных стандартом функций входят сканирование редких данных, выставление УСТРОЙСТВАМИ сигнала на ТР-штырек (безусловное или только при выдаче SR-запроса на обслуживание) и адресация МАСТЕРОМ по сигналам на ТР-штырьках в следующем цикле.

Записи в маршрутных таблицах (в СОЕДИНИТЕЛЯХ СЕГМЕНТОВ), соответствующие АДРЕСУ ГРУППЫ, равному нулю, используют для прокладки глобальной ШИРОКОЙ АДРЕСАЦИИ, ШИРОКУЮ АДРЕСАЦИЮ могут узнать и передать несколько СОЕДИНИТЕЛЕЙ СЕГМЕНТОВ, поскольку не требуется возвращать индивидуальные подтверждения. Структура, образуемая распространяющимся сигналом ШИРОКОЙ АДРЕСАЦИИ, должна быть простой древовидной структурой без пересечений. Это требование следует обеспечивать программой инициализации.

После того, как ШИРОКИЙ АДРЕС успешно прошел через всю систему, вспомогательная логика совместно с СОЕДИНИТЕЛЯМИ СЕГМЕНТОВ генерирует сигнал СИСТЕМНОГО ПОДТВЕРЖДЕНИЯ. Последующие циклы передачи данных могут использовать СИСТЕМНЫЕ ПОДТВЕРЖДЕНИЯ. Таким образом, при помощи ШИРОКОЙ АДРЕСАЦИИ могут быть выполнены стандартные операции записи или чтения любого вида сразу в группе УСТРОЙСТВ.

ШИРОКАЯ АДРЕСАЦИЯ может отнимать некоторое время, так как приходится ожидать завершения конфликтов при использовании СЕГМЕНТОВ. Однако, когда соединения в системе завершены, скорость выполнения циклов передачи данных ограничена только СИСТЕМНЫМ ПОДТВЕРЖДЕНИЕМ и временами распространения сигналов.

1.2.9. Арбитраж владения магистралью

Одной из наиболее важных характеристик многопроцессорной системы является метод предоставления управления СЕГМЕНТОМ различным МАСТЕРАМ, которые могут одновременно претендовать на владение магистралью. Схема, помогающая выполнению этой задачи, имеется в каждом независимом СЕГМЕНТЕ и называется управлением таймирования арбитража (УТА).

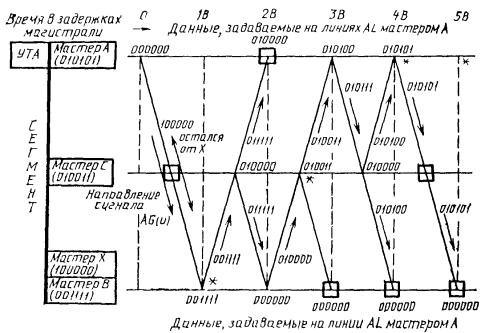

Для арбитража приоритетов в СЕГМЕНТЕ предназначены 10 магистральных линий. Каждому МАСТЕРУ присвоен уровень арбитража в виде кода из 6 битов. МАСТЕРА, желающие владеть магистралью, возбуждают линию AR - запрос на арбитраж. Если линия GK (подтверждение приема (разрешения на арбитраж) не возбуждена, УТА начинает цикл арбитража, выставляя сигнал AG - разрешение на арбитраж. Запрашивающие МАСТЕРА отвечают выставлением своих уровней арбитража на 6 линий уровня арбитража AL <5:0>. На каждой линии бит «0» поглощается битом «1». Каждый запрашивающий непрерывно сравнивает свой уровень арбитража с кодом на AL-линиях бит за битом, начиная со старшего бита. Если запрашивающий обнаруживает на магистрали бит «1», который сам он не выставил, он снимает с магистрали все свои биты меньшей значимости. Спустя время, определяемое УТА, на AL-линиях остается лишь код наивысшего заявленного уровня арбитража, в результате каждый из соревнующихся знает, выиграл он или проиграл. Если управление таймированием арбитража видит, что магистраль полностью свободна (AS = AK=WT = GK = 0), оно прекращает выдачу АС, а выигравший МАСТЕР отвечает выставлением GK и вступает во владение магистралью. МАСТЕР продолжает держать сигнал GK до тех пор, пока не решит позволить следующий цикл арбитража. МАСТЕР снимает сигналы GK обычно после последнего адресного цикла в своей серии операций, позволяя следующему МАСТЕРУ быть выбранным до того, как сам действующий МАСТЕР закончит свои циклы передачи данных.

В описанной схеме арбитража возможны два сходных протокола. В одном из них запросы на арбитраж делаются безотносительно к присутствию любых других запросов, а это ведет к возможности того, что МАСТЕРА с низким приоритетом могут не получать владение магистралью в течение неограниченно долгих периодов времени. В другом протоколе гарантированного доступа запросы на арбитраж делаются только при условии, что на линии AI (запрет запроса на арбитраж) находится логический «0». В начале цикла арбитража управление таймированием арбитража возбуждает линию AI и снимает сигнал только тогда, когда удовлетворены все запросы. В результате все запросы на арбитраж, заявленные к данному моменту времени, удовлетворяются, прежде чем может быть сделан новый запрос. МАСТЕРА могут использовать любой из протоколов и работать при этом в одном и том же сегменте, поскольку протоколы отличаются только условиями на выставление сигнала AR.

Из 64 возможных кодов приоритета код 0 не используется, так как его легко спутать с отсутствием кодов в неработающей в данный момент магистрали. Коды от 1 до 31 предназначены для использования внутри сегмента. Коды от 32 до 63 служат в качестве «системных» приоритетов, единственных для каждой из частей связанной системы. Локальные приоритеты 1 - 31 внутри данного СЕГМЕНТА должны быть единственными для каждого УСТРОЙСТВА, т.е. два УСТРОЙСТВА не должны иметь одинаковых приоритетов, однако в любом СЕГМЕНТЕ можно использовать приоритеты, уже назначенные в других СЕГМЕНТАХ. Когда СОЕДИНИТЕЛЬ СЕГМЕНТОВ соединяет МАСТЕРА с другим СЕГМЕНТОМ, уровень, используемый для арбитража во втором СЕГМЕНТЕ, обычно должен быть уровнем, присвоенным СОЕДИНИТЕЛЮ СЕГМЕНТОВ, а не уровнем действующего МАСТЕРА. Однако, если действующий МАСТЕР использовал один из системных приоритетов, СС передаст этот приоритет во второй СЕГМЕНТ, который будет освобожден для работы, поскольку системные приоритеты единственны на маршруте. Системные приоритеты могут быть полезны для предотвращения нежелательных задержек при важных ШИРОКИХ АДРЕСАЦИЯХ и могут помочь передавать важные сообщения, которые в иных условиях могли бы приостанавливаться вследствие борьбы приоритетов при прокладке пути через систему.

Прерывание текущей операции возможно, благодаря этому МАСТЕР имеет возможность удерживать магистраль, сколько он хочет. Если МАСТЕР видит сигнал AR = 1 когда AS = AK = 1, то он знает, что другие МАСТЕРА в системе заблокированы текущей операцией. Действующему МАСТЕРУ следует нормально освободить магистраль в течение приемлемого времени, чтобы позволить другим МАСТЕРАМ получить владение магистралью. Программированием следует разрешать МАСТЕРУ либо запрашивать лишь один цикл арбитража, либо задерживаться на случайное время выдержки, прежде чем снова запрашивать магистраль. Общим разрешением проблемы соревнования и тупиковых ситуаций является отказ от попытки запроса с последующим ее возобновлением после случайной выдержки времени.

1.2.10. Прерывания

Прерывание - это запрос от УСТРОЙСТВА к процессору для обслуживания или внимания. Поскольку прерывания могут пересекать границы СЕГМЕНТА и поскольку они должны нести информацию, они выполняются нормальными ФАСТБАС-операциями.

Прерывающие устройства адресуются к области управляющего регистра в интерфейсе процессора, чувствительной к прерываниям, и записывают в регистры свой собственный адрес и, возможно, другую информацию. В результате процессор имеет всю информацию, необходимую для последующего выбора и обслуживания УСТРОЙСТВА, выдавшего прерывание.

В некоторых системах большое число простых УСТРОЙСТВ, не способных ни владеть магистралью, ни выполнять операцию записи прерывания, могут нуждаться в обслуживании по запросам. Такие УСТРОЙСТВА могут возбуждать линию SR - запрос на обслуживание, за этой линией может наблюдать специально выделенное УСТРОЙСТВО обработки запросов (УОЗ). Это УСТРОЙСТВО может получить владение магистралью и найти запросившего при помощи ТР-штырьков или другими способами. УОЗ может затем само выполнить необходимое обслуживание или послать сообщение нормального прерывания по просьбе запросившего какому-нибудь другому процессору. СОЕДИНИТЕЛИ СЕГМЕНТОВ могут быть запрограммированы на пропускание запросов SR от одного СЕГМЕНТА к другому.

1.2.11. Таймирование

Соотношения между фронтами таймирующих сигналов в системе ФАСТБАС определены независимо от технологии исполнения микросхем, поэтому для гарантированной работы в конкретной среде нужны дополнительные сведения о таймировании. Сведения эти двух типов:

а) задержки сигналов, обеспечивающие правильное взаимное таймирование и достаточную длительность сигналов, чтобы они были узнаваемы;

в) лимиты времени ожидания ответов, по истечении которых мастера начинают повторную процедуру восстановления связей.

Используемый в необходимых случаях сигнал WT (ожидание) блокирует последующие таймирующие сигналы в магистрали, а также устанавливает в исходное состояние таймер ответных действий в МАСТЕРАХ. Сигнал WT может быть использован для «замораживания» состояния магистрали в целях диагностики и, в дополнение, как часть протокола, межсегментного таймирования, при котором превышение лимита времени нужно определять только для местных, а не глобальных условий.

1.2.12. Инициализация

При включении питания все УСТРОЙСТВА приводятся в пассивное состояние и откликаются лишь на ГЕОГРАФИЧЕСКУЮ АДРЕСАЦИЮ. Следовательно, перед использованием их необходимо инициализировать. Инициализация состоит в выполнении ряда операций, некоторые из которых, такие как правильная установка ЛОГИЧЕСКИХ АДРЕСОВ и загрузка маршрутных таблиц в СОЕДИНИТЕЛЕ СЕГМЕНТОВ, требуют общих знаний о всей системе и ее структуре, в то время как другие, тaкие как установка коэффициента усиления усилителя или установка счетчиков на нуль, являются специфическими для каждого УСТРОЙСТВА или группы УСТРОЙСТВ.

Для каждой системы ФАСТБАС один процессор, ХОЗЯИН, содержит полное описание системы, к которой он присоединен. Система ФАСТБАС должна быть построена таким образом, чтобы ХОЗЯИН имел доступ к каждому входящему в нее УСТРОЙСТВУ. ХОЗЯИН, знающий структуру системы, может инициализировать маршрутные таблицы в СОЕДИНИТЕЛЯХ СЕГМЕНТОВ с помощью стандартных алгоритмов, гарантируя, что правила, касающиеся маршрутов, и дерево ШИРОКИХ ОПЕРАЦИЙ, а также любые ограничения на совместимость, наложенные пользователем, соблюдаются. Программа ХОЗЯИНА для инициализации также назначает уровни арбитража для МАСТЕРА и ЛОГИЧЕСКИЕ АДРЕСА для УСТРОЙСТВ, которым они необходимы, и выполняет специальные операции данного УСТРОЙСТВА.

Процесс инициализации продолжается методично. В начале инициализируются все СОЕДИНИТЕЛИ СЕГМЕНТОВ, начиная с тех, которые находятся на том же СЕГМЕНТЕ, что и ХОЗЯИН, а затем и за его пределами. Для каждого СС ХОЗЯИН вначале обращается к ближней стороне и загружает маршрутную таблицу и уровень арбитража для операций до дальней стороны.

Затем разрешаются операции по направлению к дальней стороне, и ХОЗЯИН загружает маршрутную таблицу, а также уровень арбитража на дальней стороне, и, наконец, отпирает СС для операций в обратном направлении, а именно обратных по отношению к ХОЗЯИНУ. Это продолжается до тех пор, пока все СС не инициализируются. Затем инициализируются СЛУГИ и МАСТЕРА. Дееспособность МАСТЕРА создается в последнюю очередь, чтобы исключить возможность для МАСТЕРА попытаться войти в еще неинициализированные части системы.

Всю топологическую информацию системы ФАСТБАС также, как и данные, специфичные для инициализации каждого УСТРОЙСТВА, лучше всего содержать в базе данных, управляемой ХОЗЯИНОМ. После инициализации системы может возникнуть необходимость обратиться к этой базе данных в случае каких-либо проблем с системой или УСТРОЙСТВОМ. Например, УСТРОЙСТВА, получившие сигнал RB (оброс магистрали) требуют по крайней мере повторного «оживления», а замененные УСТРОЙСТВА-инициализации. Централизация требуемой информации и действий упрощает управление системой.

1.2.13. Средства диагностики

Благодаря тому, что все ФАСТБАС-сигналы появляются на каждой позиции КРЕЙТ-СЕГМЕНТА, в крейт можно вставить УСТРОЙСТВО, которое будет контролировать всю работу магистрали. Возможно сконструировать такие УСТРОЙСТВА, которые будут реагировать на операции определенных типов. В таком УСТРОЙСТВЕ можно запомнить историю циклов, прошедших в магистрали, для их последующего вызова и анализа.

УСТРОЙСТВО, способное выдавать сигнал WT, является простым, но мощным средством диагностики. Сигнал ожидания, помимо сброса и запрета работы таймера ответных действий в МАСТЕРАХ, запрещает любые изменения состояния 6 таймирующих сигналов: AG, GK AS, AK, DS и DK, эффективно останавливая всю работу магистрали ФАСТБАС. Благодаря этому, применяя простое испытательное оборудование, можно обследовать состояние магистрали после каждого таймирующего фронта путем снятия и повторной выдачи сигнала ожидания WT.

ГЛАВА 2. УСЛОВИЯ, ОПРЕДЕЛЕНИЯ, СОКРАЩЕНИЯ И СИМВОЛЫ

В этой главе дана интерпретация стандарта, описаны обозначения, условия относительно логических сигналов, определения, сокращения и символы, применяемые в настоящем стандарте.

2.1. Интерпретация настоящего стандарта

Пункты и абзацы стандарта со словом «должен» являются обязательными

Пункты, заключенные в рамку, являются обязательными.

Определения, относящиеся к рекомендуемой или предпочтительной практике, содержат слово «следует». Такие определения рекомендуется выполнить, если нет серьезных причин против их выполнения. Примеры или допустимые варианты обычно содержат слово «может» и оставляют свободу выбора разработчику или пользователю.

В тексте обычно применяется десятичное счисление. Если тип счисления не ясен из контекста, к двоичным числам добавляется буква b (например 00100b), а к шестнадцатиричным - буква h (например, 1A3F5h).

Чтобы соответствовать настоящему стандарту, выполняемые устройства или системы должны удовлетворять обязательным требованиям этого стандарта.

Не- ФАСТБАС-оборудование, которое не противоречит в своем действии характеристикам ФАСТБАС, определенным в этом стандарте, рассматривается как совместимое с системой ФАСТБАС.

Ни одна из частей этого стандарта не исключает использование оборудования, которое совместимо в упомянутом смысле, если даже оно не полностью соответствует стандарту.

Ни лицензий, ни других разрешений не требуется, чтобы использовать настоящий стандарт.

2.2. Обозначения и условия логических сигналов

В настоящем стандарте использованы следующие обозначения для регистров и разрядов в регистрах.

<номер бита высшего порядка : номер бита низшего порядка>

Выражение XX = N означает, что на линиях, обозначенных XX, выставлен код со значением N.

Принята положительная логика, т.е. сигнал с высоким значением обозначает логическую 1, а с низким значением - 0. Это отражается в обозначении сигнала, т.е.:

АК при высоком сигнале изображает логическую 1;

АК* при высоком сигнале изображает логический 0, иначе говоря АК* активен при низком значении.

Если ФАСТБАС реализован в ЭСЛ-логике, сигнал «Подтверждение приема адреса» можно обозначать АК, однако в системе с ТТЛ-логикой обозначение будет АК*. В логических схемах сигналы, магистрали обычно проставляют в прямоугольнике (см. рисунок).

Обычно применяемые логические графические символы соответствуют Публикации МЭК 113-7 (ГОСТ 2.743). Рекомендуется использование положительных логических символов. Применение этих символов к линиям межсоединений обычно приводит к неотрицательным выходам, соединенным с неотрицательными входами.

Следующие параметры показывают обозначения линий и сигналов:

SS все SS-линии и SS-сигналы;

SS0 SS-линия или сигнал с весом 1;

SS1 SS-линия или сигнал с весом 2;

SS2 SS-линия или сигнал с весом 4;

SS = 2 значение кода на группе SS-линий или сигналов;

SS <2:0> SS2, SS1, SS0;

SS1 = 1 логическое состояние линий SS1 или сигнала.

2.3. Определения

|

Адрес Address |

Синоним первичного адреса |

|

Адрес группы Group Address |

Старшие разряды, расположенные слева и определяющие адресное поле устройств в ФАСТБАС-адресе, которые используются для идентификации сегмента, содержащего устройство. Данному сегменту могут быть приписаны несколько адресов группы. См. базовый адрес группы. |

|

Адрес модуля (MA) Module Address (MA) |

Группа разрядов, определенная внутри адресного поля устройства в ФАСТБАС-адресе, которая идентифицирует модуль в сегменте. Адрес модуля может частично перекрывать адрес группы. |

|

Адрес следующей передачи Next Transfer Address (NTA) |

Указатель в слуге к тому регистру, который должен быть выбран во время следующей передачи данных. Запись в NTA-регистр может быть сделана во время первичного адресного цикла, а в течение вторичного адресного цикла могут быть выполнены чтение или запись. |

|

Адрес устройства (АУ) Device Address (DA) |

Идентифицирующее число разрядностью (32-m) битов, присвоенное ФАСТБАС-устройству и сопоставляемое с адресным кодом на магистрали во время цикла первичной адресации при ФАСТБАС-операции. Адрес устройства образуется из полей адреса группы и адреса модуля. Остающиеся т младших разрядов относятся к полю внутреннего адреса. |

|

Адресный цикл Address Cycle |

Синоним первичного адресного цикла. |

|

Базовый адрес группы Base Group Address |

Значение адреса группы GP, которое используется для географической адресации сегменту. Нормально наинизший GP, присвоенный сегменту. |

|

Ближняя сторона (соединителей сегментов СС или БСС) Near Side (of an SI or BI) |

Проход в СС или БСС, который электрически ближе к действующему мастеру. |

|

Буферизированный соединитель сегментов (БСС) Buffered Interconnect BI |

Устройство, которое обеспечивает соединение сегментов таким образом, что ФАСТБАС-протокол в одном сегменте не синхронизирован с протоколом в другом сегменте. |

|

Слуга Slave |

Устройство, которое отвечает мастеру в соответствии с ФАСТБАС-протоколом. |

|

Мастер Master |

Устройство, которое способно заявлять операцию и управлять ею в сегменте в соответствии с |

|

Владение магистралью Mastership |

ФАСТБАС-протоколом. Мастер владеет магистралью, когда - получил право управлять сегментом и выдал сигнал GK или AS. |

|

Время разброса задержек Skew Time |

Минимальное время, на которое после выдачи информационных и/или управляющих сигналов должен быть задержан сигнал таймирования, чтобы учесть различия во временах распространения сигналов в ФАСТБАС-сегменте. |

|

Вспомогательная логика (ВЛ) Ancillary Logic (ANC) |

Логическая схема, присутствующая в каждом сегменте, но не являющаяся частью какого-либо устройства. Операции арбитража, географической адресации, системного подтверждения и управление работой / остановом выполняются вспомогательной логикой, которая может также содержать терминаторы сегмента. |

|

Вспомогательный разъем модуля (ВРМ) Module Auxiliary Connector |

Стандартный разъем, который монтируется над сегментным разъемом модуля на печатной плате модуля. |

|

Вторичный адрес Secondary Address |

Адрес, используемый внутри устройства. Он определяется во вторичном адресном цикле установкой NTA-регистра устройства после первичного адресного цикла. |

|

Вторичный адресный цикл Secondary Address Cycle |

Цикл данных, в котором мастер использует линии AD адрес/данные для загрузки вторичного адреса в NTA-регистр устройства. |

|

Выдержка Retry Period |

Интервал времени, в течение которого мастер, не получив ответа, ожидает, прежде чем снова начать операцию. Этот интервал должен быть случайным, чтобы избежать зависаний в системе. |

|

Географический адрес (ГА) Geografical Address (QA) |

Первичный адрес устройства, основанный на физическом (географическом) положении модуля и задаваемый кодированными штырьками сегментного разъема или (на кабель-сегменте) переключаемым вручную регистром. В крейт-сегменте географический адрес нуль имеет крайняя правая позиция, если смотреть на крейт спереди. Адрес возрастает на единицу при переходе влево на соседнюю позицию. |

|

Дальняя сторона (соединителей сегментов) Far Side (of an SI or BI) |

Проход в соединителях СС или БСС, который электрически более удален от действующего мастера. |

|

Дополнительная плата модуля Module Supplementary Board |

Любая плата в ФАСТБАС-модуле, не имеющая прямого соединения с крейт-сегментом. |

|

Древовидная структура Tree Structure |

Комплекс соединенных сегментов без контуров (пересечений связей). |

|

ESONE |

Многонациональный комитет, представляющий европейские ядерные лаборатории. Он выпустил первоначальный стандарт КАМАК и сотрудничает с NIM в эксплуатации и развитии системы КАМАК, а также в разработке системы ФАСТБАС. |

|

Задняя плата Backplane |

Кросс-плата со схемой (обычно печатной) в тыльной части крейта, которая через свои разъемы присоединяет модули и образует крейт-сегмент. |

|

Зарезервировано Reserved |

Линия магистрали, штырьки разъема, коды, биты и т.п., сохраняемые для определения их функций комитетом NIM в будущем. Они не должны использоваться до такого определения. |

|

Защитный буфер Protective Buffer |

Произвольный буфер в слуге, состоящий из одного слова, который всегда содержит копию самых последних данных, выставленных или полученных слугой. |

|

Интерфейс процессора (ИП) Processor Interface |

Интерфейсное устройство между внешним процессором и ФАСТБАС-сегментом. |

|

Кабель-сегмент Cable Segment KAMAK CAMAC |

ФАСТБАС-сегмент, состоящий из кабеля с соответствующими разъемами для присоединения устройств. Международная стандартизованная модульная приборная и цифровая интерфейсная система, определенная стандартом IEEE Std 583 и соответствующая документам EUR 4100 и IEC 516. |

|

Крейт Crate (FASTBUS CRATE) |

Каркас для ФАСТБАС-модулей, объединяемых крейтом-сегментом. |

|

Крейт-сегмент Crate Segment |

ФАСТБАС-сегмент, который состоит из задней платы, укрепленной на ФАСТБАС-крейте и имеющей разъемы для присоединения множества ФАСТБАС-модулей к магистрали. |

|

Лимит времени ожидания Wait Timeout Period |

Время, в течение которого мастер ждет после получения сигнала WT, прежде чем прекратить соединение. |

|

Логический адрес Logical Address |

Первичный адрес из 32 битов, состоящий из адреса устройства и внутреннего адреса. Не зависит от положения устройства в сегменте. |

|

Маршрутная таблица Route Table |

Список адресов групп, распознаваемых соединителем сегментов для пропускания операций к сегменту, соединенному с дальней стороной. |

|

Минимальный промежуток между импульсами Minimum Pulse Down Timt |

Чтобы любое устройство могло обнаружить состояние «0» сигнала между двумя сигналами «1», состояние «0» должно длиться не менее времени заднего фронта импульса, которое зависит от характеристик магистрали. |

|

Модуль Module |

Любое ФАСТБАС-устройство, которое может быть помещено в ФАСТБАС-крейт, присоединено к крейт-сегменту и соответствует обязательным требованиям этого стандарта к модулю. |

|

NIM |

1. Комитет, действующий под покровительством Министерства энергетики США и связанный с Национальным бюро стандартов. Комитет выпустил стандарты на приборную систему NIM, одобрил применение системы КАМАК, сотрудничает с комитетом ESONE в развитии и распространении КАМАК. 2. Стандартизованная модульная приборная система, состоящая из модулей NIM и бинов (крейтов) NIM, определенная докладом TID-20893 Министерства энергетики США. |

|

Нулевая операция Null Operation |

Первичный адресный цикл, не сопровождаемый циклом передачи данных. Операция определяет, имеется ли в системе устройство, способное реагировать на выданный первичный адрес. Нулевая операция может быть использована для забронирования соединителя сегментов с целью проведения серии операций при заблокированном арбитраже. |

|

Область адресов данных Data Space |

См. область адресов регистров управления и состояний. |

|

Область адресов регистров управления и состояний CSR Space |

Циклом первичного адреса при помощи кода на управляющих линиях MS (выбор режима) может быть определена одна из двух раздельных адресных областей в устройстве: область адресов регистров и состояний, а также область адресов данных. Область CSR содержит регистры для управления устройством и регистры для информации о состоянии устройства. Их размещение и применение определяются стандартом ФАСТБАС. |

|

Операция Operation |

Первичный адресный цикл в совокупности с одним или несколькими циклами передачи данных и с заключающей последовательностью задних фронтов сигналов. |

|

Операция прерывания Interrupt Operation |

ФАСТБАС-операция записи в устройство, обслуживающее прерывания, извещающая, что запрашивающий требует внимания. |

|

Операция с фиксированным адресом Address Locked Operation |

Операция, направленная к одному первичному адресу, содержащая сочетание циклов чтения и записи; может также включать передачу блока. |

|

Очистка цикла Cleanup Data Cycle |

Цикл данных, который не сопровождается передачей данных, а предназначен только для выключения драйверов слуги: AD (адрес/данные), РА (четность) и РЕ (разрешение контроля по четности). |

|

Первичный адрес Primary Address |

Адрес, присвоенный устройству, посредством которого мастер способен установить связь с устройством или с подразделением устройства. Типы первичного адреса: логический, географический и широкий. |

|

Первичный адресный цикл Primary Address Cycle |

Часть ФАСТБАС-операции, в которой мастер адресуется к слуге через линии AD адрес/данные. Тип адреса определяется сигналами на управляющих линиях ЕС и MS. Цикл начинается сигналом на линии AS строб адреса и заканчивается, когда мастер получает сигнал подтверждения приема адреса на линии АК. Во время первичного адресного цикла могут быть переданы логический, географический и широкий адреса. |

|

Передача блока Block Transfe |

Часть ФАСТБАС-операции, при которой мастер либо посылает данные присоединенному слуге, либо получает от него данные при каждом фронте сигнала DS строб данных. Слуга подтверждает прием или посылает данные при каждом фронте сигнала DK. |

|

Передача блока, принудительная Pipelined Transfer |

Часть ФАСТБАС-операции, при которой мастер или посылает данные присоединенному слуге, или вынуждает его выдавать данные на. каждом фронте сигнала DS строб данных. Слуга подтверждает прием или передачу данных при помощи каждого фронта сигнала DK-подтверждение приема данных. Мастер не ожидает подтверждения от слуги и выдает следующий фронт сигнала DS в своем темпе. |

|

Переключатель работа / останов (ПРО) Run/Halt Switch (RH) |

Схемный переключатель, нормально приводимый в действие от планки, запирающей модули в крейте, или от схемы управления таймированием арбитража и кабель-сегменте. Переключатель останавливает передачи в магистрали, чтобы можно было безопасно вставлять или вынимать модули, не влияя на состояние других модулей в сегменте. |

|

Печатная плата модуля (ППМ) Module Circuit Board |

Печатная плата, служащая основой для схемной части ФАСТБАС-модуля. |

|

Подготовленный мастер Pending Master |

Мастер, который участвовал в самом последнем цикле арбитража и выиграл. В результате он вступит во владение магистралью, когда действующий мастер освободит магистраль. |

|

Подтверждение Handshake |

Взаимосвязанный обмен сигналами между мастером и слугой с подтверждением передачи информации. |

|

Позиция Position, Slot |

Позиция модуля в крейте. Номер позиции соответствует географическому адресу. |

|

Поле внутренних адресов (IA) Internal Address Field |

Группа младших разрядов (расположенных справа и примыкающих левой стороной к адресному полю устройств), определяющая в ФАСТБАС-адресе адреса внутри модуля. Циклы вторичной адресации позволяют увеличить количество ячеек памяти сверх того количества, которое определено полем внутренних адресов. |

|

Последовательность завершения Termination Sequence |

Процесс, с помощью которого связка AS/AK разрушается. |

|

Превышение лимита времени Timeout |

Превышение лимита времени имеет место, когда таймер ответных действий по истечении установленного времени прерывает операцию, не дождавшись ожидаемого события. Контроль лимита времени предохраняет систему от неопределенного ожидания в случаях ошибки или неисправности. |

|

Присоединенный слуга Attached Slave |

Присоединенный слуга - это такой слуга, который в предыдущем первичном адресном цикле узнал свой адрес, тип адреса и в результате будет участвовать в последующем цикле передачи данных. |

|

Протокол гарантированного доступа Assured Access Protocol |

Потенциальный мастер работает в протоколе гарантированного доступа, если он, обнаружив выданный сигнал АI-запрет запроса на арбитраж, не выдает запрос AR и, таким образом, не будет участвовать в последующих циклах арбитража до тех пор, пока все устройства, уже выдавшие AR, не получат право на владение магистралью и не завершат свои операции. |

|

Процессор-хозяин (ПХ) Host Processor (HP) |

Обрабатывающий и управляющий процессор, предназначенный для всеобщего наблюдения за системой ФАСТБАС. Содержит детальные сведения о топологии системы. |

|

Регистр управления и состояний Control and Status Register (CSR) |

Регистр, используемый для управления операцией устройства и/или записи статуса операции. Он доступен при обращении к отдельной области адресов регистров управления и статуса ФАСТБАС-устройства. Регистр CSR-0, обязательный для всех устройств, содержит код идентификации устройства, заданный его производителем, ряд битов статуса устройства, а также некоторые биты, определяемые производителем. |

|

Режим прослеживания ошибки на маршруте Route Tracing Mode |

Режим операции соединителя сегментов, в которой вырабатывается реакция на диагностику ошибки вместо нормального прохождения операции. |

|

Расширенный сегмент Extended Segment |

Множественность крейт-сегментов, к которым обеспечен доступ через тот же самый адрес группы. В отличие от операций на сегментах, соединенных соединителями сегментов, независимые операции на каждом из сегментов, являющихся частью расширенного сегмента, никогда не протекают параллельно. В зависимости от метода реализации, могут существовать некоторые ограничения, касающиеся размещения мастеров. В зависимости от расположения модулей на расширенном сегменте, некоторые широкие операции могут быть неприменимы или могут требовать специальной интерпретации. |

|

Расширитель сегмента Segment Extender (SE) |

Устройство для соединения двух сегментов с целью формирования расширенного сегмента или его части. |

|

Сегмент Segment |

Определенное средство для передачи информации, функционирующее в соответствии с ФАСТБАС-протоколом, к которому могут быть присоединены ФАСТБАС-устройства. Сегмент способен работать автономно и сообщаться с другими сегментами через соединители сегментов (СС). |

|

Сегментный разъем модуля Module Segment Connector |

Стандартный разъем, который монтируется на ФАСТБАС-модуле и сочленяется с сегментным разъемом крейта. |

|

Серия операций с заблокированным арбитражем Arbitration Lokeed Sequence |

Серия операций, выполняемых одним мастером, направленная к нескольким различным первичным адресам, которая не может быть прервана ни одним из других мастеров, поскольку действующий мастер не разрешает арбитраж магистрали. |

|

Сканирование редких данных (СРД) Sparse Data Scan (SDS) |

Технический прием, при помощи которого множества модулей, содержащих мало данных, могут быть эффективно опрошены без соединения с каждым модулем из тех, которые потенциально могут содержать информацию, но не содержат ее в данный момент. |

|

Системное подтверждение System Handshake |

Подтверждение в широкой операции, при котором сигнал подтверждения получается от последнего сегмента адресуемой системы, а не от индивидуального устройства. |

|

Соединенная система Connected System |

Все сегменты соединенной системы способны связываться непосредственно друг с другом через СС. Следует заметить, что вследствие определения путей передачи сообщений маршрутными таблицами, сегменты системы, соединенные электрически при помощи СС, не соединены также логически в употребляемом здесь смысле. |

|

Соединитель Interconnect |

См. соединитель сегментов и буферизованный соединитель сегментов. |

|

Соединитель сегментов (СС) Segment Interconnect (SI) |

Устройство, которое осуществляет такое соединение двух сегментов, при котором выполнение в них ФАСТБАС-протокола синхронизировано. Когда операция пропускается через СС, он действует как слуга на ближней стороне и как мастер на дальней стороне. |

|

Соединитель сегментов активный Active Segment Interconnect |

Соединитель сегментов является активным, когда он выдает сигнал AS=1 в сегмент, присоединенный к дальней стороне. |

|

Соединитель сегментов завладевший Reserved Segment Interconnect |

Соединитель сегментов является завладевшим, если он завладел магистралью сегмента, присоединенного к дальней стороне, и выдал сигнал GK= 1 в этот сегмент. |

|

Таймер ответных действий Response Timer |

Таймер внутри слуги или соединителя сегментов, предназначенный для прекращения операции, которая не закончилась в течение заданного достаточного интервала времени. |

|

Узорный выбор устройств Pattern Select |

Широкий адрес, специфичный тем, что все устройства, замечающие широкую адресацию, остаются связанными с мастером только в случае, если их ТР-штырьки заявлены в течение последующего цикла записи данных. |

|

Управление географической адресацией (УГА) Geografical Address Control (ПАС) |

Логическая схема на каждом сегменте для генерации и контроля сигналов, предназначенных для осуществления географической адресации. |

|

Управление таймированием арбитража (УТА) Arbitration Timing Control (АТС) |

Логическая схема в каждом сегменте, предназначенная для наблюдения и генерации сигналов управления арбитражем, работой / остановом и системным подтверждением при широкой операции. Является частью вспомогательной логики. |

|

Устройство Device |

Любое устройство, способное к присоединению к сегменту и соответствующее обязательным требованиям ФАСТБАС-протокола. |

|

Устройство обработки запросов (УОЗ) Service Request Handler (SRH) |

Мастер, назначенный для наблюдения за линией SR запросов на обслуживание в сегменте или в группе сегментов. Если SR=1, MOЗ запрашивает владение магистралью и после его получения определяет, какой модуль или какие модули выдали SR=1, либо опросом, либо при помощи широкой операции. Затем МОЗ может сам обслужить поступившие запросы или послать прерывание другим устройствам по поручению модулей, выдавших SR. Сигнал SR обычно выдается только теми модулями, которые мало способны к владению магистралью. |

|

Устройство обслуживания прерываний (УОП) Interrupt Service Device (ISO) |

Процессор или другое устройство, которое может отвечать на операцию прерывания. |

|

ФАСТБАС FASTBUS |

Стандартизованная быстродействующая магистрально-модульная многопроцессорная информационно-измерительно-управляющая система, определяемая настоящим стандартом. |

|

ФАСТБАС-протокол FASTBUS Protocol |

Формат и последовательность управляющих сообщений и сообщений данных в системе ФАСТБАС. Форматы определяются назначением сигнальных линий магистрали ФАСТБАС. Последовательности определяются ФАСТБАС-операциями. |

|

Цепная связь Daisy Chain |

Соединение на задней панели между соседними позициями, которое позволяет передавать информацию между соседними модулями независимо от ФАСТБАС-протокола. |

|

Цикл арбитража Arbitration Cycle |

Процесс, определяющий следующего мастера, который будет владеть магистралью. Цикл начинается управлением таймированием арбитража и завершается, когда выигравший мастер получает право на владение магистралью. |

|

Цикл записи (запись) Write Cycle (Write) |

Цикл, при котором поток данных направлен от мастера к слуге (слугам). |

|

Цикл данных Data Cycle |

Часть ФАСТБАС-операции, в которой мастер или посылает данные к присоединенному слуге, или получает данные от него. Цикл начинается с выдачи мастером фронта сигнала DS-строб данных и оканчивается с получением от слуги фронта сигнала DK-подтверждение приема данных. |

|

Цикл считывания (чтение) Read Cycle (Read) |

Цикл, в котором поток данных направляется от слуги (слуг) к мастеру. |

|

Четность (для ФАСТБАС) Parity (for Fastbus) |

Добавленный к ФАСТБАС-слову бит, значение которого выбирается так, чтобы сделать общее число битов «1» (включая бит четности) нечетным. Он применяется для проверки ошибок, поскольку прием четного числа битов «1» свидетельствует об ошибке в передаче. |

|

Широкая операция Broadcast (Broadcast Operation) |

Операция, направленная к одному или нескольким слугам в одном или нескольких сегментах. |

|

Широкая операция глобальная Global Broadcast |

Широкая операция с теми слугами во всех сегментах многосегментной системы, которые могут быть достигнуты из сегмента с действующим мастером. |

|

Широкая операция, линейная Linear Broadcast |

Широкая операция с подгруппой сегментов, охватываемых глобальной широкой операцией. Подгруппа может быть определенным сегментом или располагаться до или после определенного сегмента. |

|

Широкая операция, локальная Local Broadcast |

Широкая операция в пределах только лишь действующего сегмента. |

|

Широкая операция с устройствами заданного класса Device Class Broadcast |

Избирательная широкая операция, определяемая регистром CSR-7. В последующих циклах отвечает лишь устройство заранее назначенного класса. |

|

Широкий адрес Broadcast Address |

Первичный адрес, выставляемый мастером при широкой операции. |

2.4. Буквенные обозначения

|

В оригинале |

В переводе (русские подчеркнуты) |

||

|

A |

Asynchronous (Type of Line) |

А |

Асинхронный (тип линии) |

|

AD |

Address/Data |

АД |

Адрес/данные |

|

AG |

Arbitration Grant |

AG |

Разрешение на арбитраж |

|

AI |

Arbitration Request Inhibit |

AI |

Запрет запроса на арбитраж |

|

AK |

Address Acknowledge |

АК |

Подтверждение приема адреса |

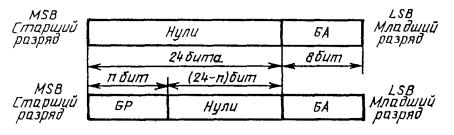

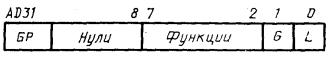

|